# GRAPHIC PROCESSORS

**DATABOOK**

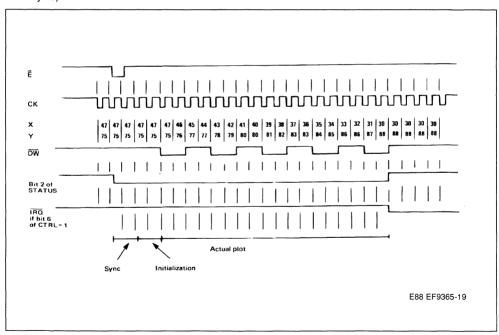

1<sup>st</sup> EDITION

# GRAPHIC PROCESSORS

**DATABOOK**

1st EDITION

**MARCH 1989**

## **TABLE OF CONTENTS**

| INTRODUCTION                                    | Page | 4   |

|-------------------------------------------------|------|-----|

| GENERAL INDEX                                   |      | 5   |

| PRODUCT GUIDE                                   |      | 7   |

| ALPHANUMERICAL and SEMI-GRAPHIC CRT CONTROLLERS |      | 11  |

| GRAPHICS CONTROLLERS                            |      | 105 |

| COLOR PALETTE                                   |      | 213 |

| APPLICATION NOTES                               |      | 247 |

#### INTRODUCTION

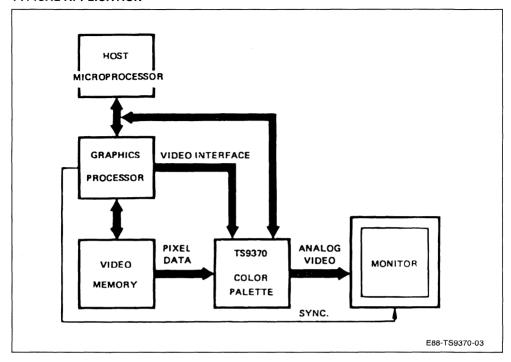

The SGS-THOMSON Graphics data book contains comprehensive data on three groups of graphics products: alphanumeric/semigraphics processors, full graphics processors and colour palettes. The optimised price/performance characteristics of the proven HMOS 2 technology, coupled with SGS-THOMSON's six years of successful participation in the graphics market, makes these products particularly suitable for low- to mid-range applications such as video games, home computers and CAD workstations.

The alphanumeric/semigraphic range is based around the highly successful EF9345 architecture. For applications requiring flexible character display with simple graphics support, these devices provide a low-cost, single-chip solution that includes a built-in character generator and attribute controller.

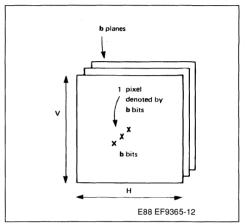

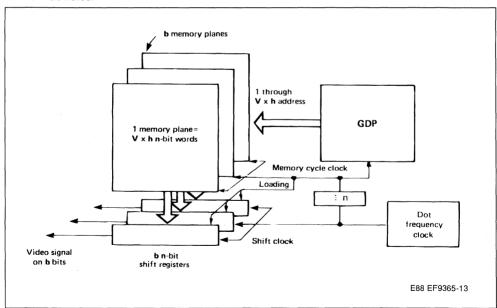

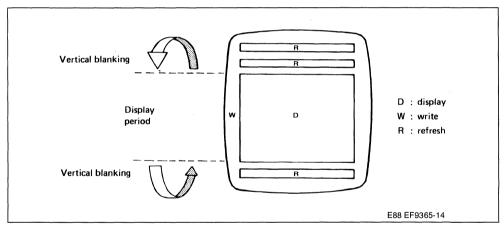

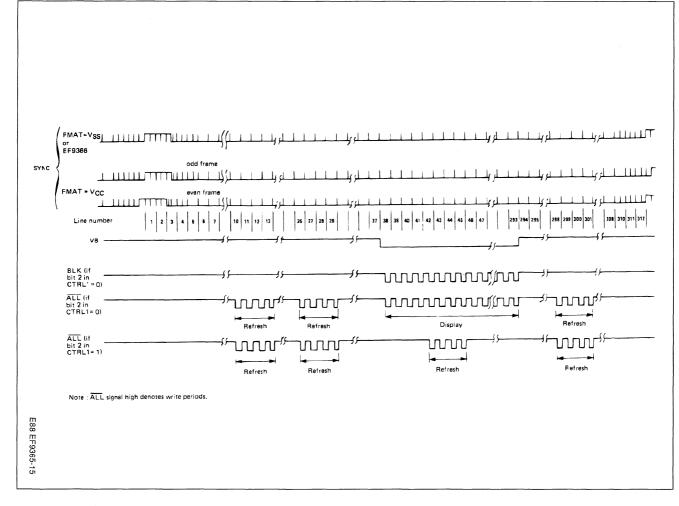

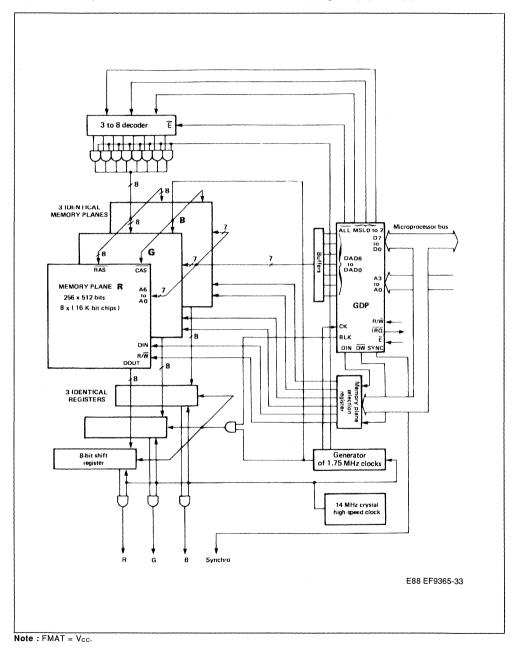

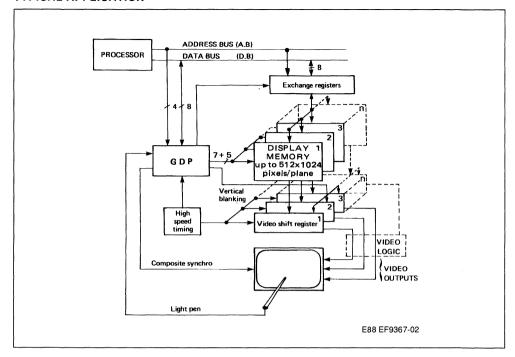

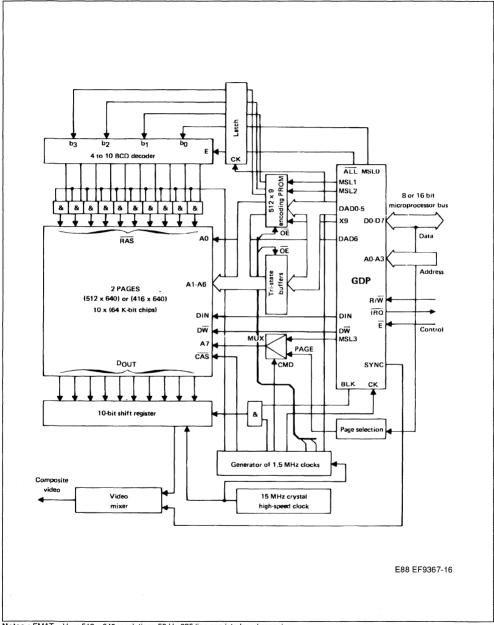

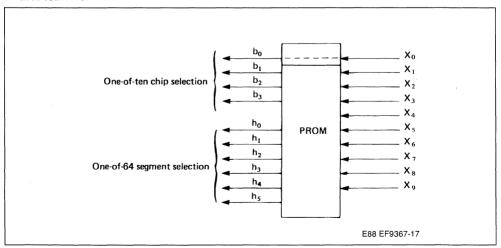

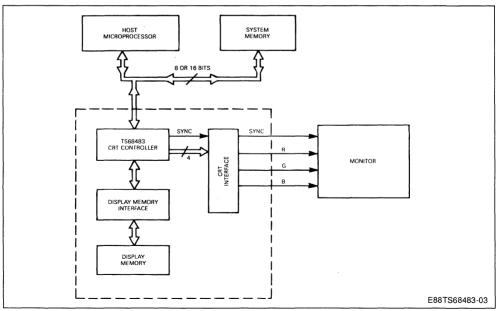

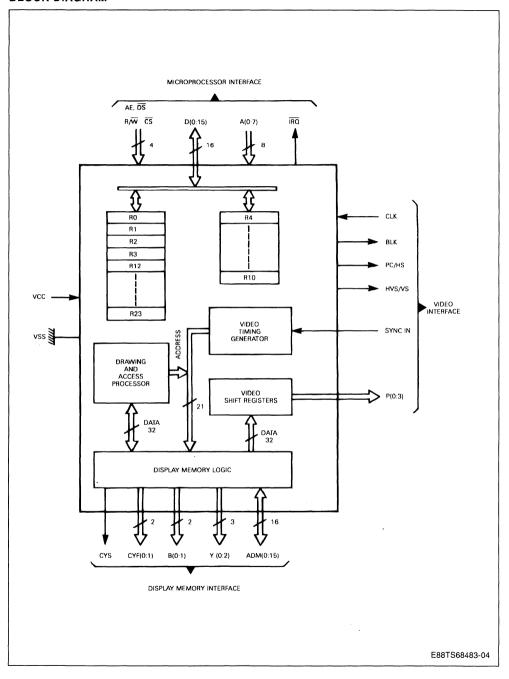

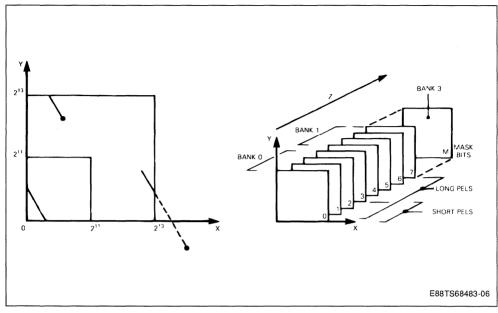

For applications requiring direct pixel addressing, with screen resolutions from  $256 \times 256$  up to  $2048 \times 2048$ , SGS-THOMSON offers several products based on the established EF9367 and the TS68483 advanced graphics processor. With integral drawing processors and character generators, these products combine high performance with cost-effectiveness.

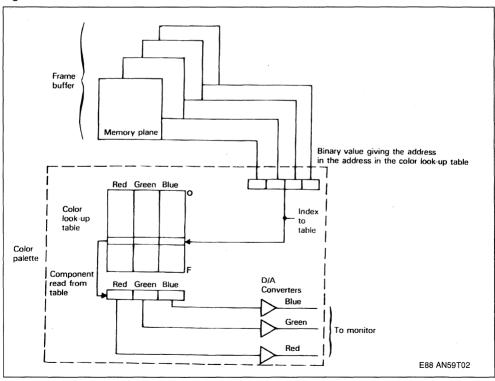

Colour palette devices are now widely used to increase the number of displayable colours and to provide a direct interface with monitors. SGS-THOMSON is established in the low-end market with a number of devices that allow 16 of 4096 colours to be selected.

### **GENERAL INDEX**

| PRODUCT CUIPE                         | raye |

|---------------------------------------|------|

| PRODUCT GUIDE SELECTION GUIDE         |      |

| GELECTION GOIDE                       | . 3  |

| ALPHANUMERIC and SEMI-GRAPHIC         |      |

| CTR CONTROLLERS                       |      |

| EF9345TS9347                          |      |

| 109047                                | 03   |

| GRAPHICS CONTROLLERS                  |      |

| EF9365/EF9366                         |      |

| EF9367                                |      |

| TS68483                               | 171  |

| COLOR PALETTE                         | 213  |

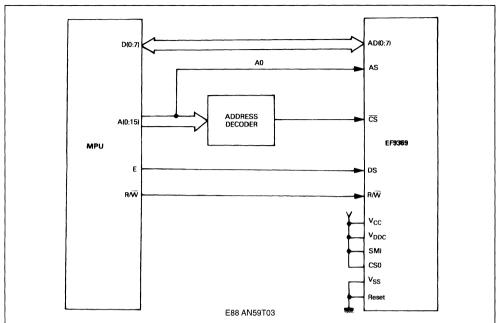

| EF9369                                | 215  |

| TS9370                                | 231  |

| APPLICATION NOTES                     |      |

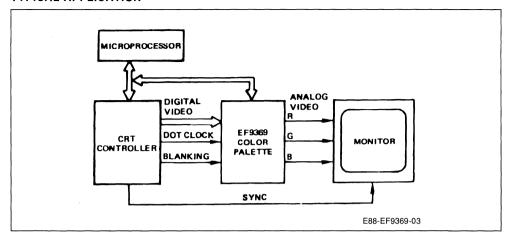

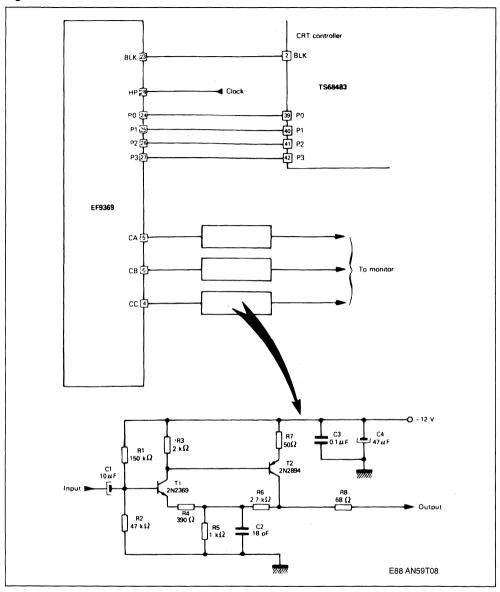

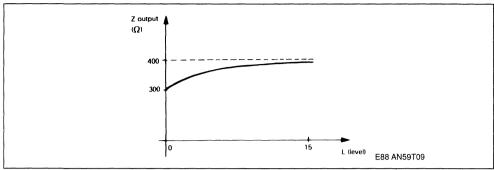

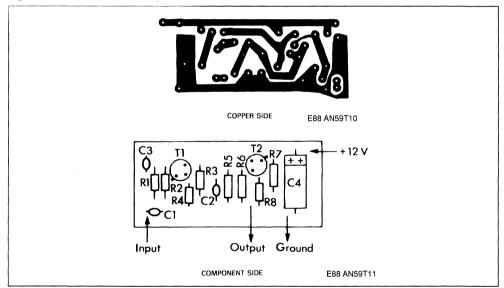

| EF9369 COLOR PALETTE                  |      |

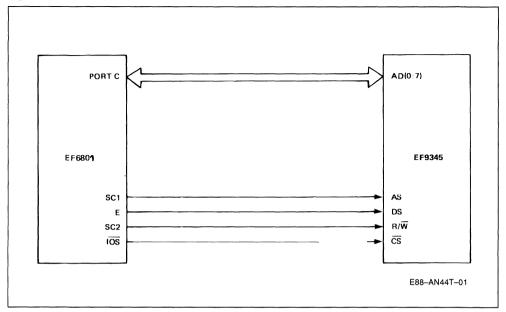

| EF9345 GENERAL APPLICATION PRINCIPLES | 261  |

# PRODUCT GUIDE

#### **ALPHANUMERIC and SEMI-GRAPHIC CRT CONTROLLERS**

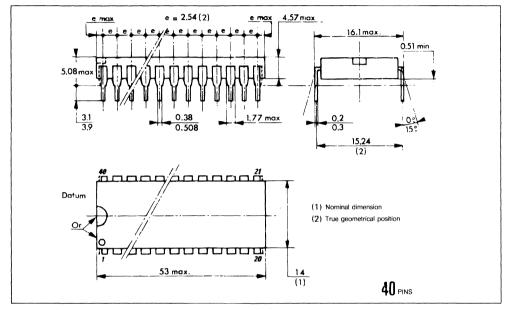

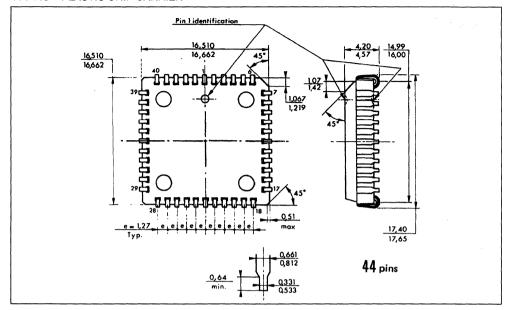

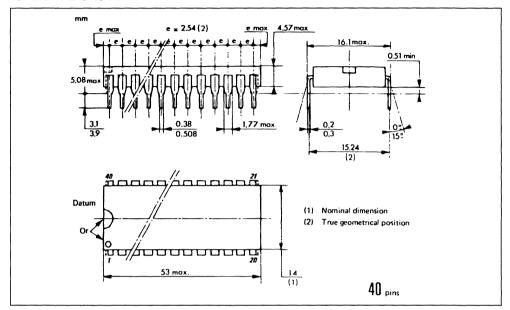

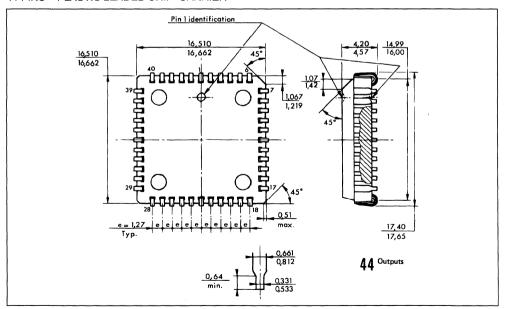

| Part Number | Description                                                                                                                                                                               | Format                                  | Package         | Page |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------|------|

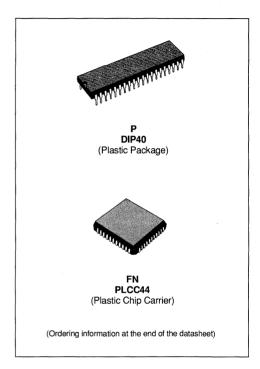

| EF9345      | Single Chip Color CRT Controller On-Chip Attributes Controller On-Chip Character Generator R,G,B,I Video Shift Registers Page Memory up to 16K×8 Bits                                     | 25/21 Rows<br>of 40 or 80<br>Characters | DIP40<br>PLCC44 | 13   |

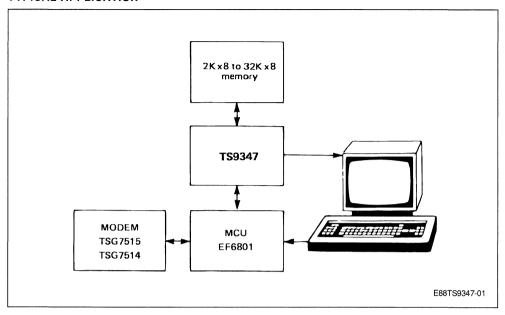

| TS9347      | Single Chip Color or B/W CRT Controller On-Chip Attributes Controller On-Chip Character Generator R,G,B,I Video Shift Registers Analog Output: 8 Grey Levels Page Memory up to 32K×8 Bits | 25/21 Rows<br>of 40 or 80<br>Characters | DIP40<br>PLCC44 | 63   |

#### **GRAPHICS CONTROLLERS**

| Part Number      | Description                                                                                                                                                                        | Format                               | Package | Page |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------|------|

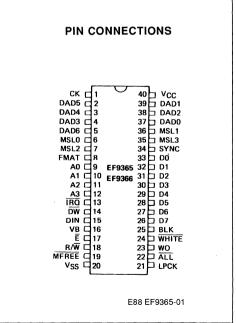

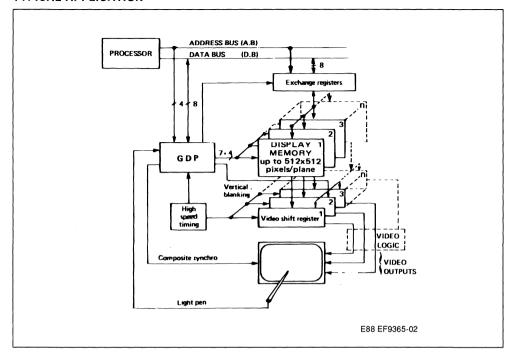

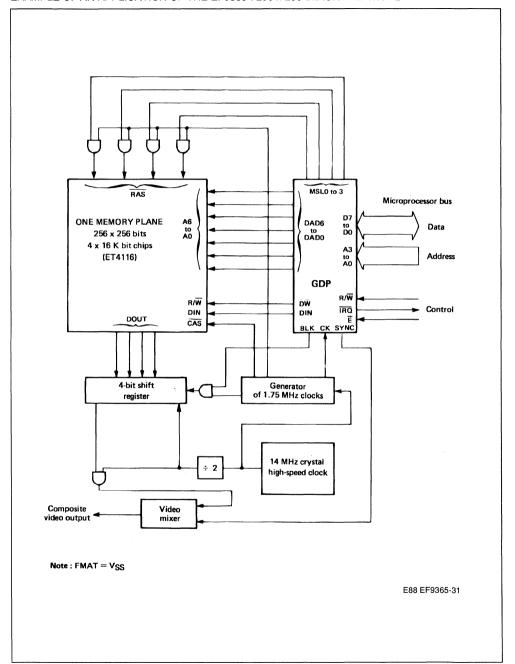

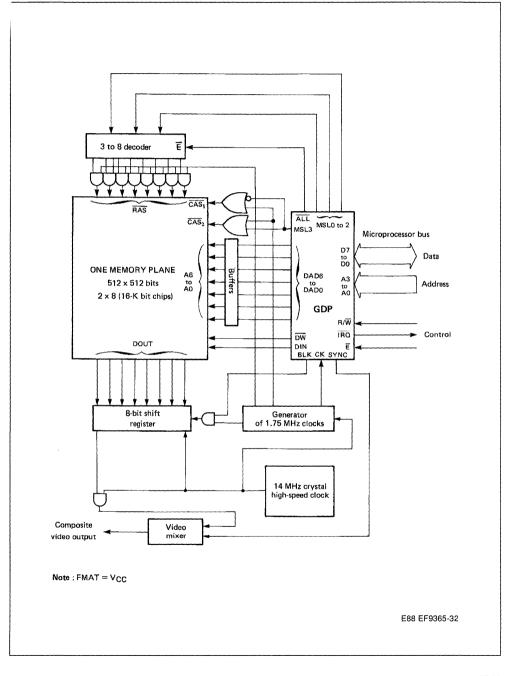

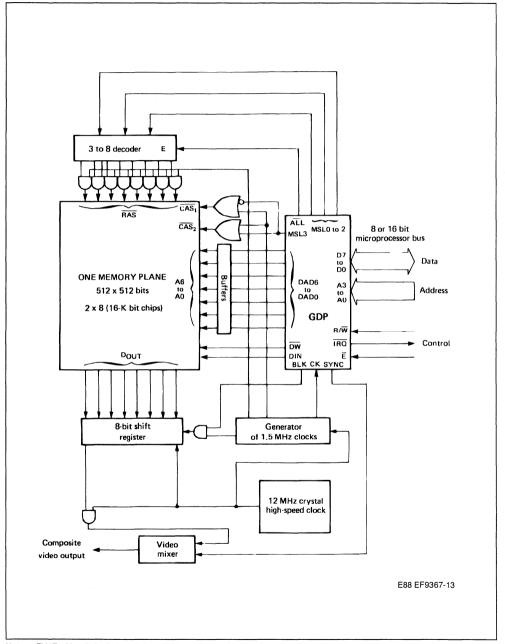

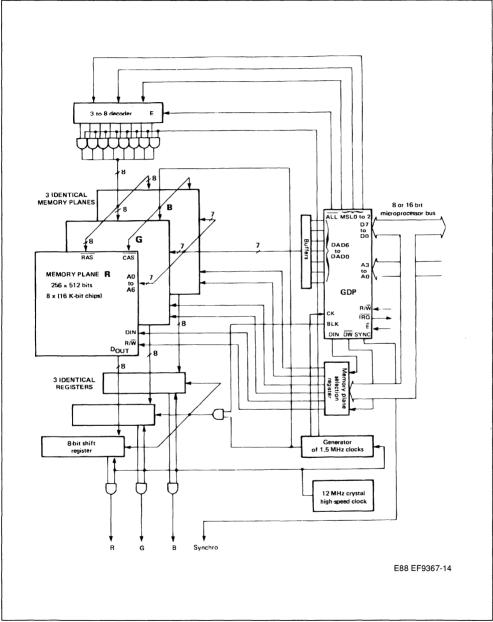

| EF9365<br>EF9366 | Graphics Coprocessor DRAMs Interface On-Chip ASCII Character Generator High-Speed Vector Drawing                                                                                   | 512(256) × 512<br>Pixels<br>50 Hz    | DIP40   | 107  |

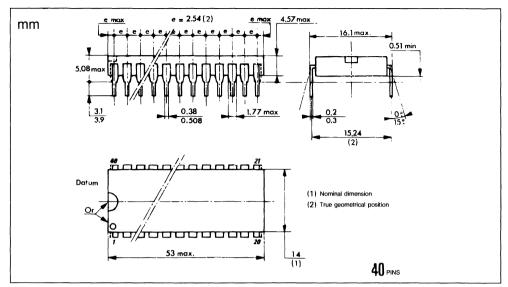

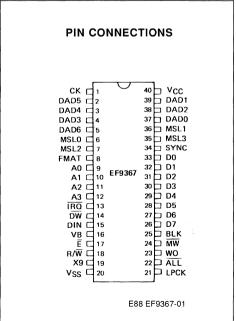

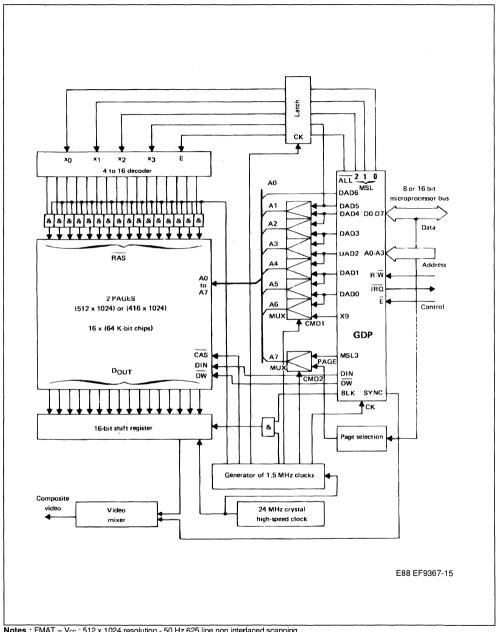

| EF9367           | Graphics Coprocessor DRAMs Interface On-Chip ASCII Character Generator High-Speed Vector Drawing                                                                                   | 512 x 1024<br>Pixels<br>50 Hz, 60 Hz | DIP40   | 137  |

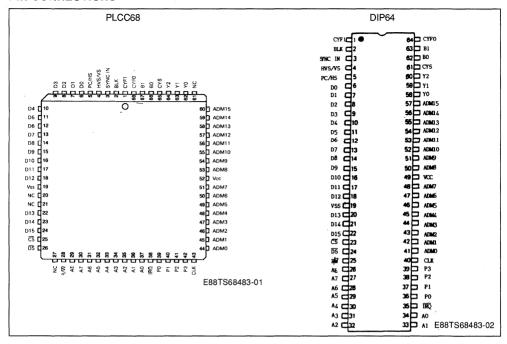

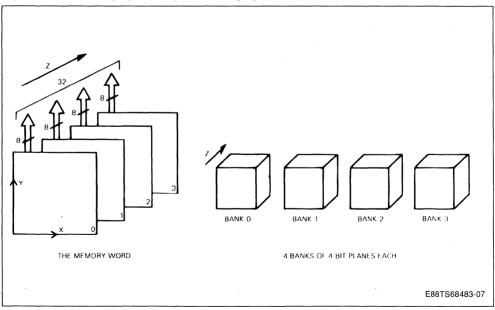

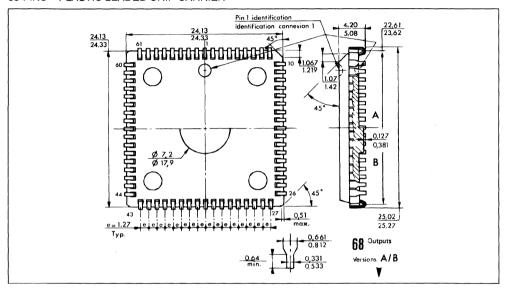

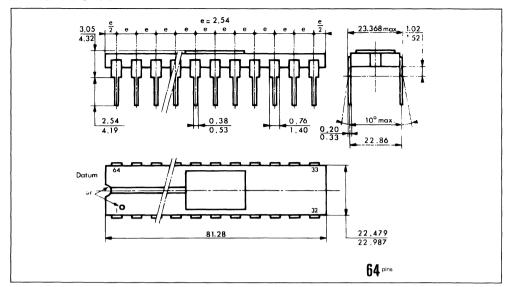

| TS68483          | Alphanumeric and Graphic Drawing Capabilities Upto 256 Colors Four Video Shift Registers For Video rate Less than 18 Md/s Command Set: Vector, Arc, Circle Area Filling, Character | 2048 × 2048<br>8-Bit Pixels          | DIP64   | 171  |

#### **COLOR PALETTE**

| Part Number | Description                                                            | Format                  | Package         | Page |

|-------------|------------------------------------------------------------------------|-------------------------|-----------------|------|

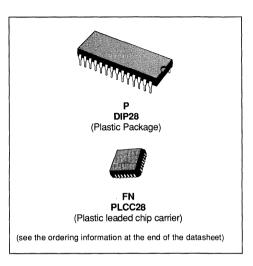

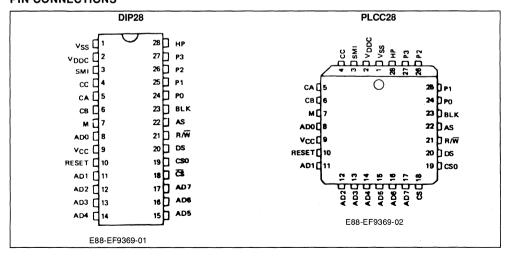

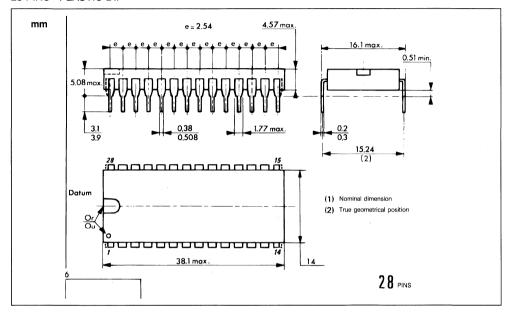

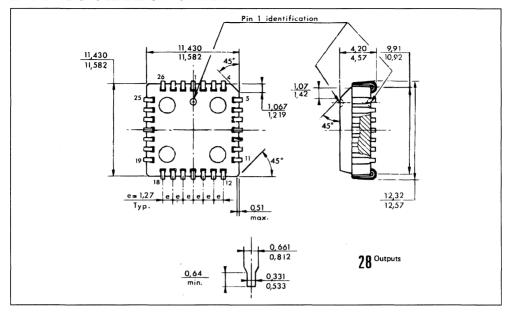

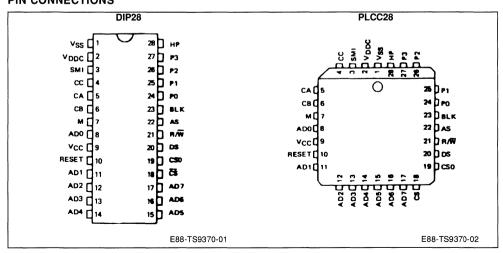

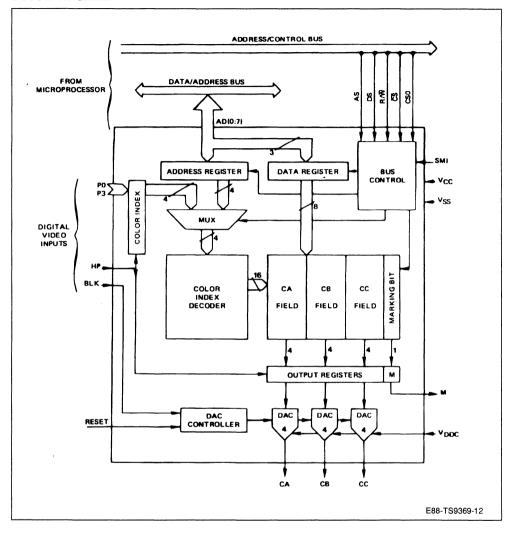

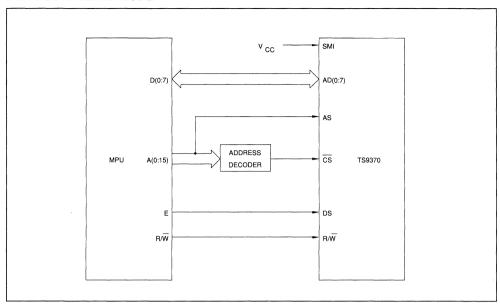

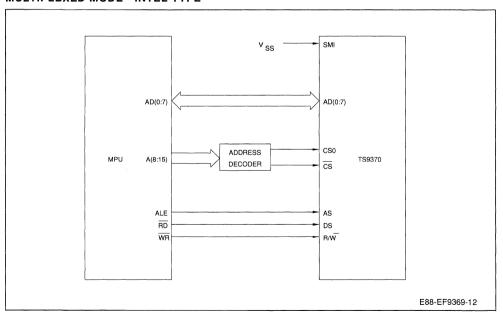

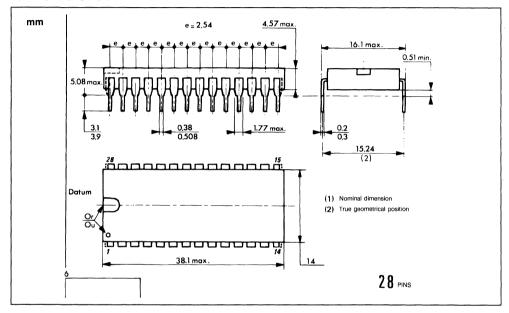

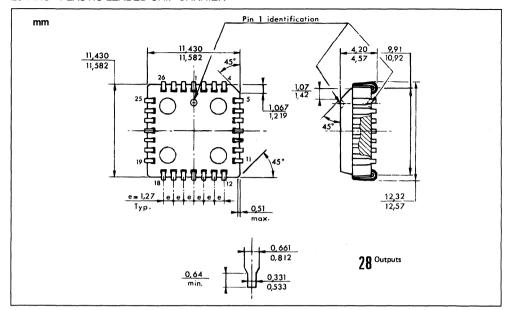

| EF9369      | 4-Bit DACs with Gamma Law Correction<br>Marking Bit<br>Upto 30 Mdots/s | 16 Colors<br>Among 4096 | DIP28<br>PLCC28 | 215  |

| TS9370      | 4-Bit DACs<br>Marking Bit<br>Upto 45 Mdots/s                           | 16 Colors<br>Among 4096 | DIP28<br>PLCC28 | 231  |

# ALPHANUMERIC and SEMI-GRAPHIC CRT CONTROLLERS

# HMOS2 SINGLE CHIP SEMI-GRAPHIC DISPLAY PROCESSOR

- SINGLE CHIP LOW-COST COLOR CRT CON-TROLLER

- TV STANDARD COMPATIBLE (50 Hz or 60 Hz)

- 2 SCREEN FORMATS:

- 25 (or 21) ROWS OF 40 CHARACTERS

- 25 (or 21) ROWS OF 80 CHARACTERS

- ON-CHIP 128 ALPHANUMERIC AND 128 SE-MI-GRAPHIC CHARACTER GENERATOR THREE STANDARD OPTIONS AVAILABLE FOR ALPHANUMERIC SETS

- EASY EXTENSION OF USER DEFINED AL-PHANUMERIC OR SEMI-GRAPHIC SETS (> 1 K characters)

- 40 CHARACTERS/ROW ATTRIBUTES: foreground and background color, double height, double width, blinking, reverse, underlining, conceal, insert, accentuation of lower case characters

- 80 CHARACTERS/ROW ATTRIBUTES: Underlining, blinking, reverse, color select

- PROGRAMMABLE ROLL-UP, ROLL DOWN, AND CURSOR DISPLAY

- ON-CHIP R, G, B, I VIDEO SHIFT REGISTERS

- EASY SYNCHRONIZATION WITH EXTERNAL VIDEO SOURCE : ON-CHIP PHASE COMPA-BATOR

- ADDRESS/DATA MULTIPLEXED BUS DI-RECTLY COMPATIBLE WITH STANDARD MICROCOMPUTERS SUCH AS 6801, 6301, 8048, 8051

- ADDRESSING SPACE: 16 K x 8 OF GENERAL PURPOSE PRIVATE MEMORY

- EASY USE OF ANY LOW COST MEMORY COMPONENTS: ROM, SRAM, DRAM

- UPWARD COMPATIBLE WITH EF9340/41 CHIP SET

#### DESCRIPTION

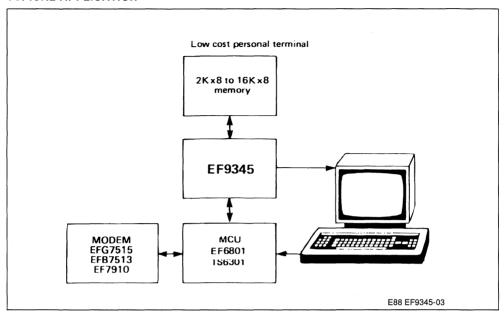

The EF9345, new advanced color CRT controller, in conjunction with an additional standard memory package allows full implementation of the complete display control unit of a color or monochrome low-cost terminal, thus significantly reducing IC cost and PCB space.

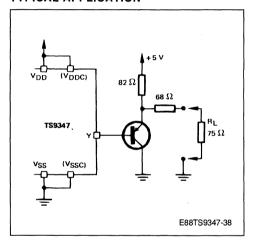

#### TYPICAL APPLICATION

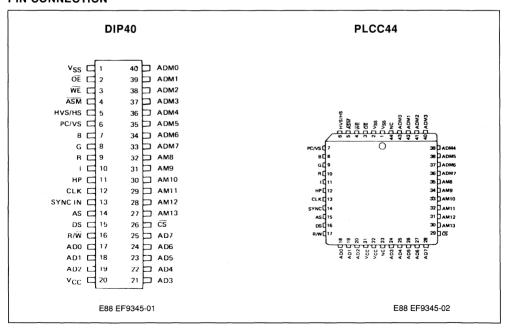

#### PIN CONNECTION

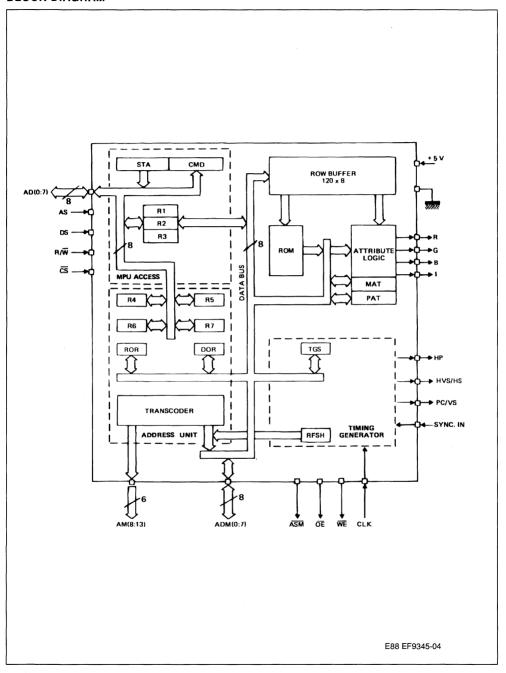

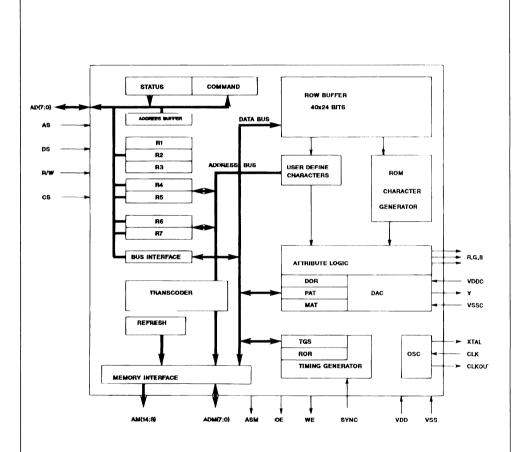

#### **BLOCK DIAGRAM**

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol            | Parameter                   | Value        | Unit |

|-------------------|-----------------------------|--------------|------|

| V <sub>CC</sub> * | Supply Voltage              | - 0.3 to 7.0 | V    |

| V <sub>in</sub> * | Input Voltage               | - 0.3 to 7.0 | V    |

| TA                | Operating Temperature Range | 0 to + 70    | °C   |

| T <sub>stg</sub>  | Storage Temperature         | 55 to + 150  | °C   |

| P <sub>Dm</sub>   | Max Power Dissipation       | 0.75         | W    |

<sup>\*</sup> With respect to Vss.

Stresses above those hereby listed may cause permanent damage to the device. The ratings are stress ones only and functional operation of the device at these or any conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect reliability. Standard MOS circuits handling procedure should be used to avoid possible damage to the device.

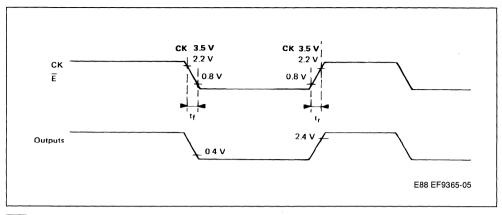

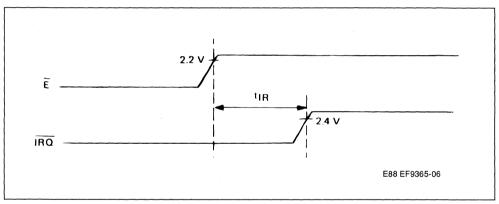

#### **ELECTRICAL CHARACTERISTICS** ( $V_{CC} = 5.0 \text{ V} \pm 5 \text{ %}, V_{SS} = 0, T_A = 0 \text{ to } 70 \text{ °C}$ )

| Symbol           | Parameter                                                                                               | Min.     | Тур. | Max.            | Unit   |

|------------------|---------------------------------------------------------------------------------------------------------|----------|------|-----------------|--------|

| Vcc              | Supply Voltage                                                                                          | 4.75     | 5    | 5.25            | ٧      |

| V <sub>IL</sub>  | Input Low Voltage                                                                                       | - 0.3    | _    | 0.8             | ٧      |

| V <sub>IH</sub>  | Input High Voltage CLK Other Inputs                                                                     | 2.2<br>2 |      | V <sub>CC</sub> | V<br>- |

| lin              | Input Leakage Current                                                                                   | _        | _    | 10              | μΑ     |

| V <sub>OH</sub>  | Output High Voltage ( $I_{load} = -500 \mu A$ )                                                         | 2.4      | _    | -               | V      |

| V <sub>OL</sub>  | Output Low Voltage $I_{load} = 4$ mA ; AD (0:7), ADM (0:7), AM (8:13) $I_{load} = 1$ mA ; Other Outputs |          | _    | _               | ٧      |

| P <sub>D</sub>   | Power Dissipation                                                                                       | _        | 250  | _               | mW     |

| Cin              | Input Capacitance                                                                                       | _        | _    | 15              | рF     |

| I <sub>TSI</sub> | Three State (off state) Input Current                                                                   |          | _    | 10              | μΑ     |

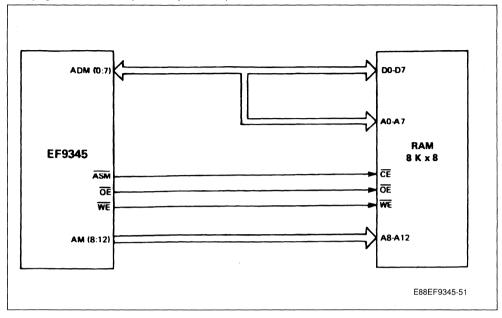

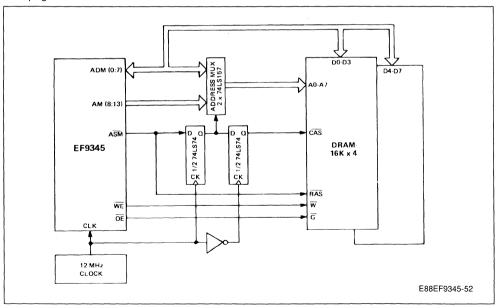

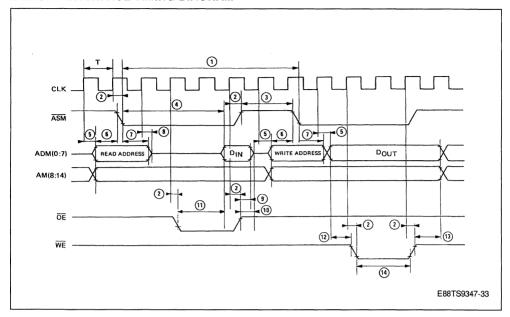

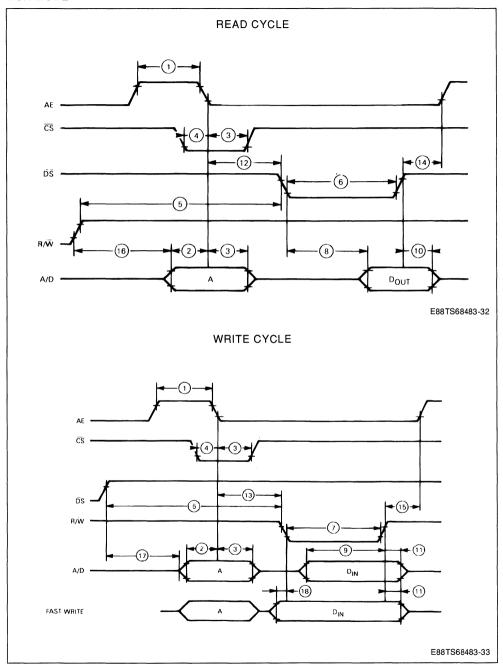

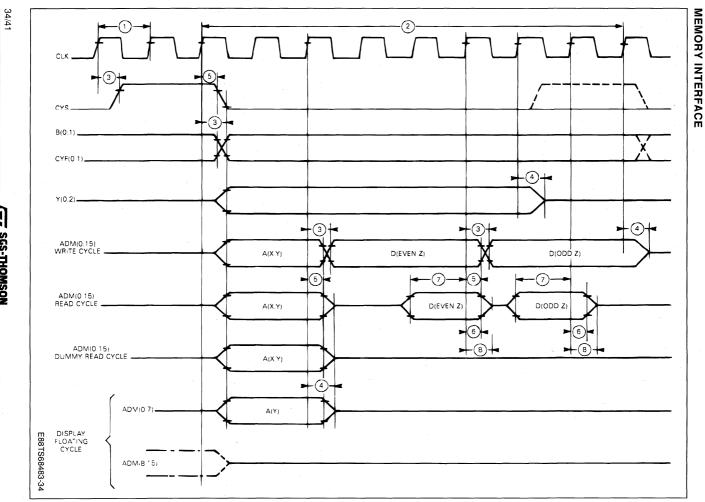

#### **MEMORY INTERFACE**

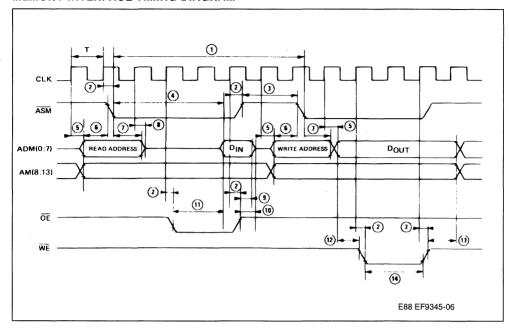

$V_{\text{CC}}=5.0~V\pm5$  %,  $T_{\text{A}}=0^{\circ}$  to + 70 °C. Clock :  $f_{\text{in}}=12$  MHz ; Duty Cycle 40 to 60 % ;  $t_{\text{r}},\,t_{\text{f}}<5$  ns Reference Levels :  $V_{\text{IL}}=0.8~V$  and  $V_{\text{IH}}=2~V,\,V_{\text{OL}}=0.4~V$  and  $V_{\text{OH}}=2.4~V.$

| Symbol            | ldent.<br>Number | Parameter                                                     | Min. | Тур. | Max. | Unit |

|-------------------|------------------|---------------------------------------------------------------|------|------|------|------|

| telel             | 1                | Memory Cycle Time                                             | _    | 500  | _    | ns   |

| t <sub>D</sub>    | 2                | Output Delay Time from CLK Rising Edge (ASM, OE, WE)          | -    | _    | 60   | ns   |

| tehel             | 3                | ASM High Pulse Width                                          | 120  | _    | _    | ns   |

| t <sub>ELDV</sub> | 4                | Memory Access Time from ASM Low                               | _    | _    | 290  | ns   |

| t <sub>DA</sub>   | 5                | Output Delay Time from CLK Rising Edge (ADM (0:7), AM (8:13)) | _    | _    | 80   | ns   |

| tavel             | 6                | Address Setup Time to ASM                                     | 30   | _    | -    | ns   |

| telax             | 7                | Address Hold Time from ASM                                    | 55   | -    | -    | ns   |

| t <sub>CLAZ</sub> | 8                | Address Off Time                                              | -    | -    | 80   | ns   |

| t <sub>GHDX</sub> | 9                | Memory Hold Time                                              | 10   | _    | _    | ns   |

| toz               | 10               | Data Off Time from OE                                         | _    | _    | 60   | ns   |

| t <sub>GLDV</sub> | 11               | Memory OE Access Time                                         | _    | _    | 150  | ns   |

| t <sub>QVWL</sub> | 12               | Data Setup Time (write cycle)                                 | 30   | _    | _    | ns   |

| twHQX             | 13               | Data Hold Time (write cycle)                                  | 30   | _    | _    | ns   |

| twLWH             | 14               | WE Pulse Width                                                | 110  | _    | _    | ns   |

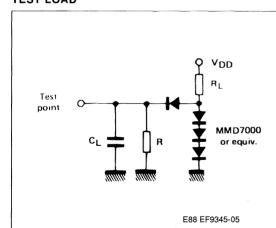

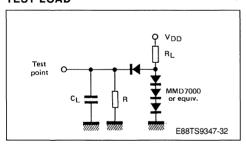

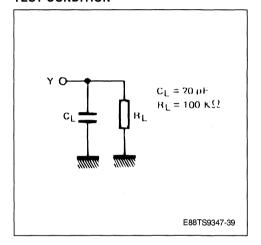

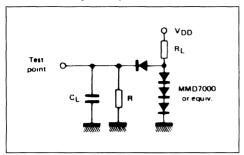

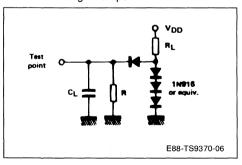

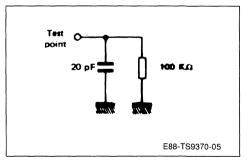

#### **TEST LOAD**

| Symbol | AD (0:7), AM (8:13)<br>ADM (0:7) | Other<br>Outputs |

|--------|----------------------------------|------------------|

| С      | 100 pF                           | 50 pF            |

| RL     | 1 ΚΩ                             | 3.3 KΩ           |

| R      | 4.7 ΚΩ                           | 4.7 ΚΩ           |

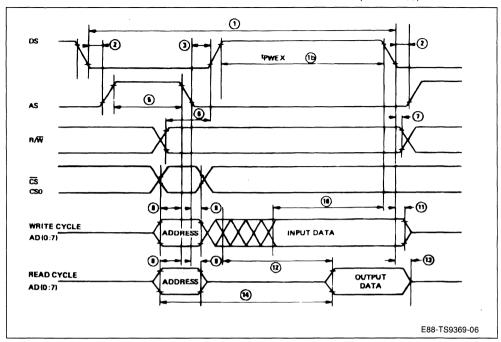

#### MEMORY INTERFACE TIMING DIAGRAM

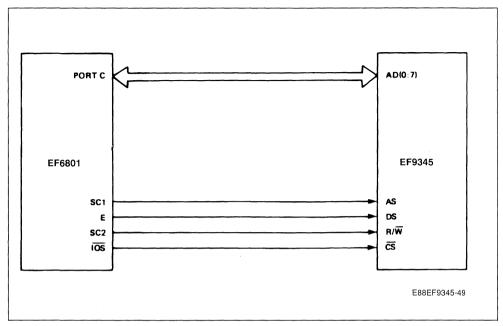

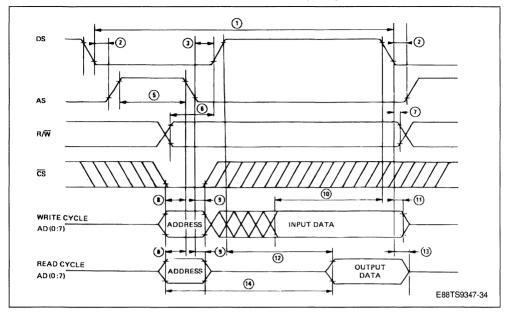

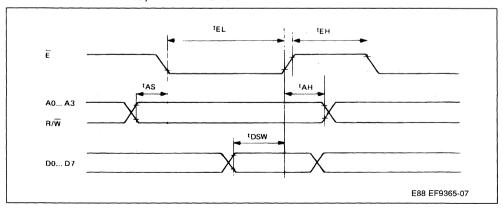

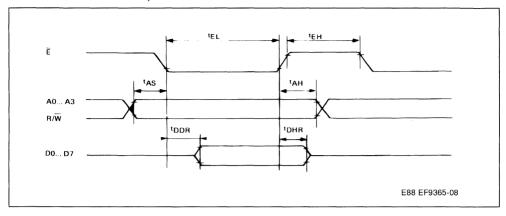

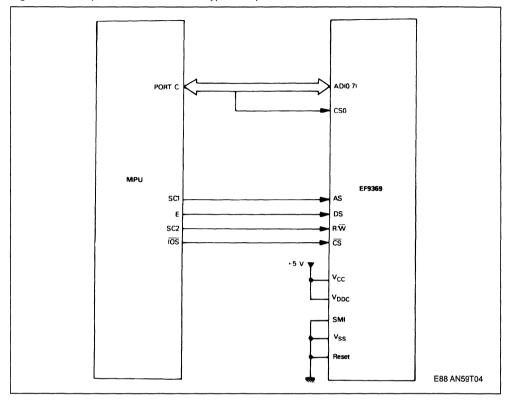

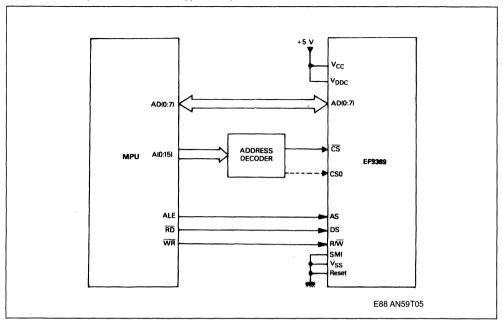

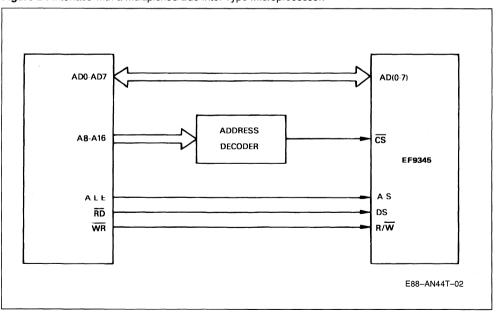

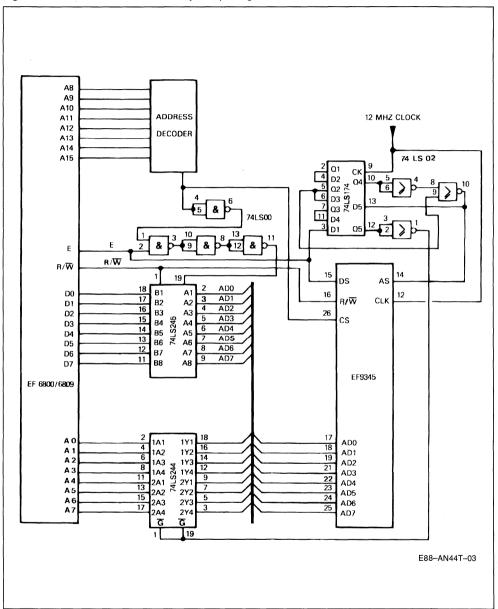

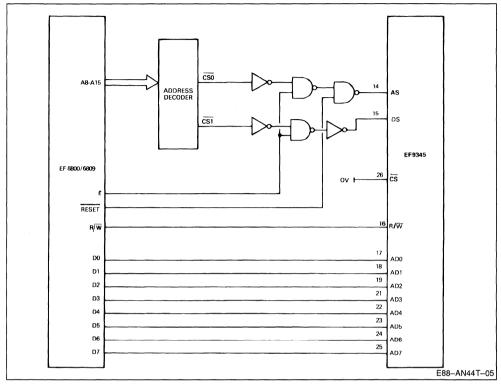

#### MICROPROCESSOR INTERFACE

EF9345 is motel compatible. It automatically selects the processor type by using AS input to latch to state of the DS input.

No external logic is needed to adapt bus control signals from most of the common multiplexed bus microprocessors.

| EF9345    | 6801                              | INTEL Family |

|-----------|-----------------------------------|--------------|

|           | Timing 1                          | Timing 2     |

| AS        | AS                                | ALE          |

| DS<br>R/W | DS, Ε <u>,</u> φ 2<br>R/ <b>W</b> | RD           |

| R/W       | R/W                               | WR           |

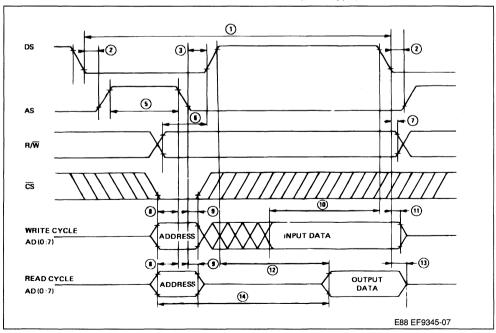

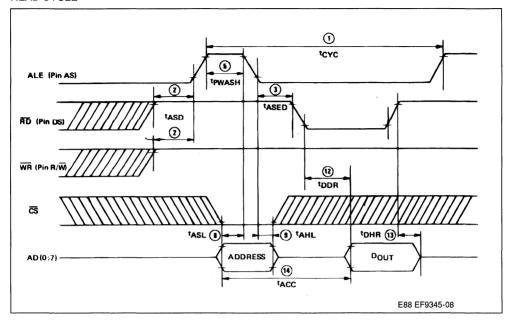

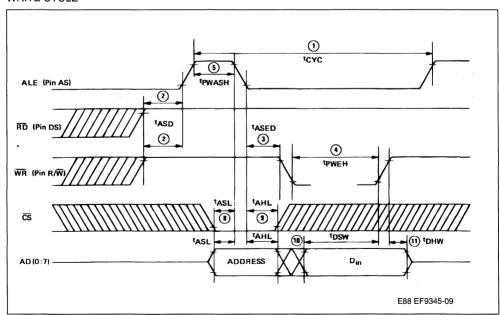

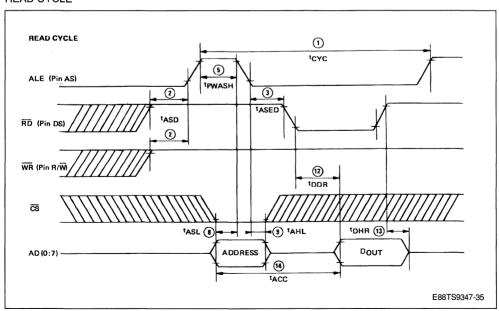

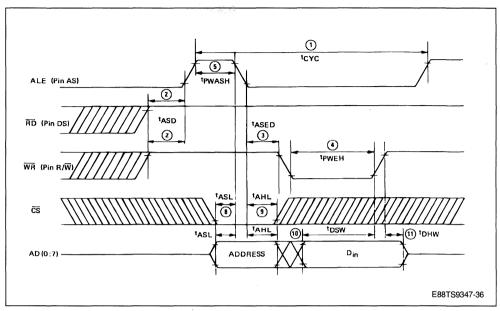

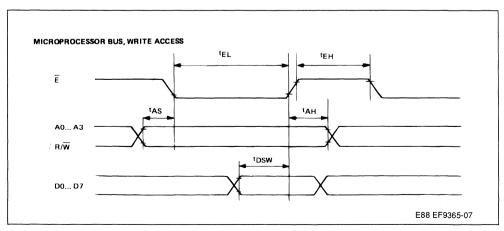

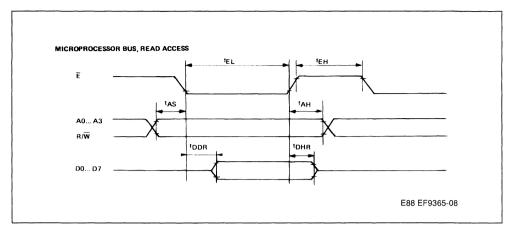

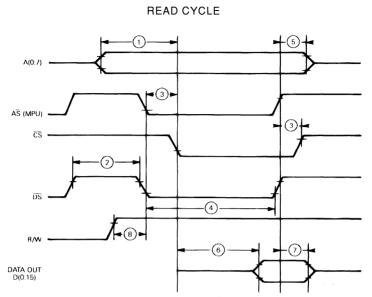

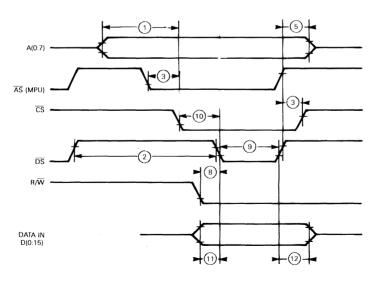

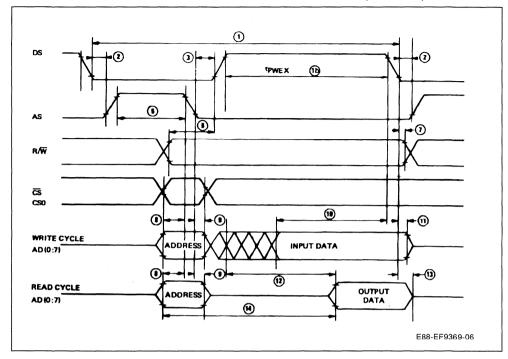

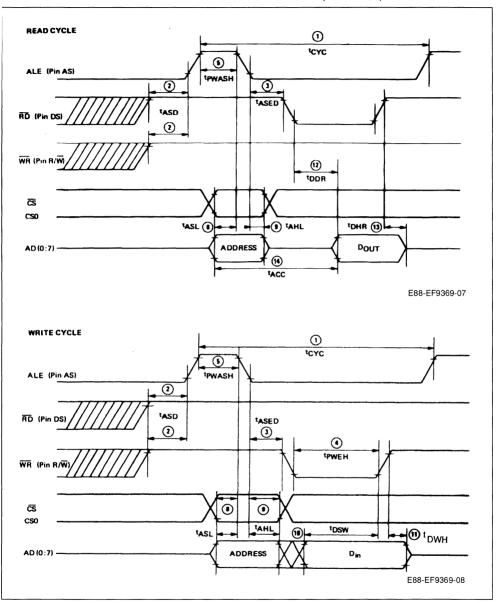

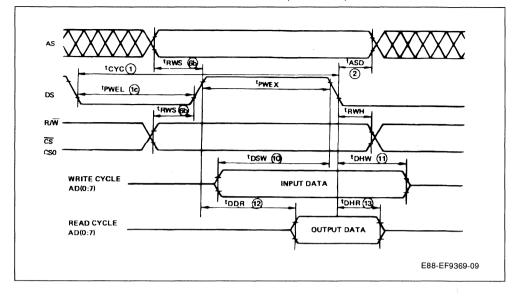

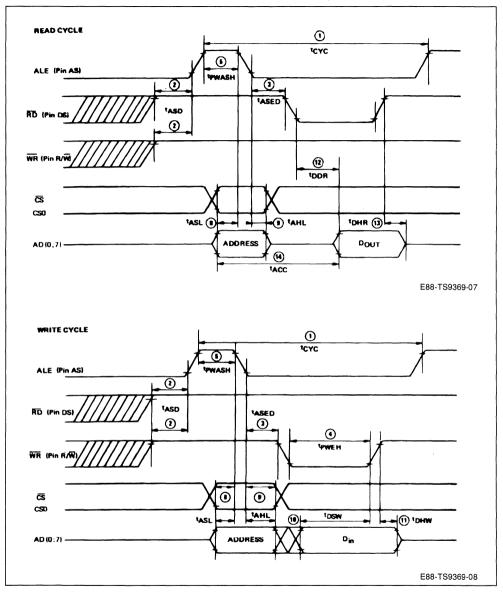

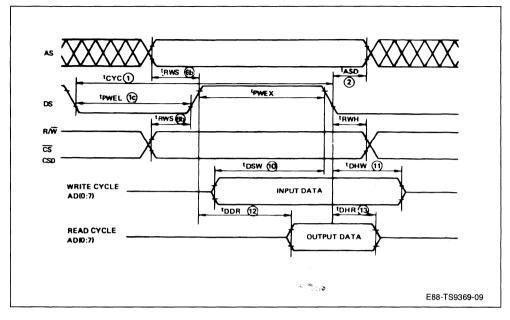

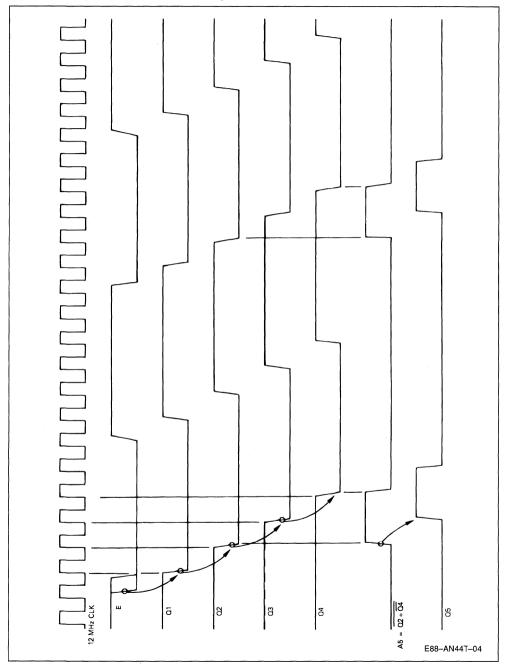

#### MICROPROCESSOR INTERFACE TIMING AD (0:7), AS, DS, $R\overline{W}$ , $\overline{CS}$

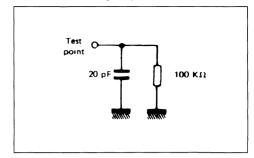

$V_{CC}$  = 5.0  $\pm$  5 %,  $T_A$  = 0° to + 70 °C,  $C_L$  = 100 pF on AD (0:7) Reference Levels :  $V_{IL}$  = 0.8 V and  $V_{IH}$  = 2 V on All Inputs ;  $V_{OL}$  = 0.4 V and  $V_{OH}$  on All Outputs.

| Symbol           | ldent.<br>Number | Parameter                                                             | Min. | Тур. | Max. | Unit |

|------------------|------------------|-----------------------------------------------------------------------|------|------|------|------|

| tcyc             | 1                | Cycle Time                                                            | 400  | _    | -    | ns   |

| tasp             | 2                | DS Low to AS High (timing 1) DS High or R/W High to AS High (tming 2) | 30   | _    | _    | ns   |

| tased            | 3                | AS Low to DS High (timing 1) AS Low to DS Low or R/W Low (timing 2)   | 30   | _    | _    | ns   |

| tpweh            | 4                | Write Pulse Width                                                     | 200  | _    | -    | ns   |

| tpwash           | 5                | AS Pulse Width                                                        | 100  | _    | _    | ns   |

| t <sub>RWS</sub> | 6                | R/W to DS Setup Time (timing 1)                                       | 100  | -    | -    | ns   |

| t <sub>RWH</sub> | 7                | R/W to DS Hold Time (tIming 1)                                        | 10   | _    | -    | ns   |

| tasL             | 8                | Address and CS Setup Time                                             | 20   | -    | _    | ns   |

| t <sub>AHL</sub> | 9                | Address and CS Hold Time                                              | 20   |      |      | ns   |

| t <sub>DSW</sub> | 10               | Data Setup Time (write cycle)                                         | 100  | _    | _    | ns   |

| t <sub>DHW</sub> | 11               | Data Hold Time (write cycle)                                          | 10   | _    | _    | ns   |

| t <sub>DDR</sub> | 12               | Data Access Time from DS (read cycle)                                 | -    | -    | 150  | ns   |

| t <sub>DHR</sub> | 13               | DS Inactive to High Impedance State Time (read cycle)                 | 10   | _    | 80   | ns   |

| tACC             | 14               | Address to Data Valid Access Time                                     | _    | _    | 300  | ns   |

#### MICROPROCESSOR INTERFACE TIMING DIAGRAM 1 (6801 type)

#### MICROPROCESSOR INTERFACE TIMING DIAGRAM 2 (INTEL type)

#### **READ CYCLE**

#### WRITE CYCLE

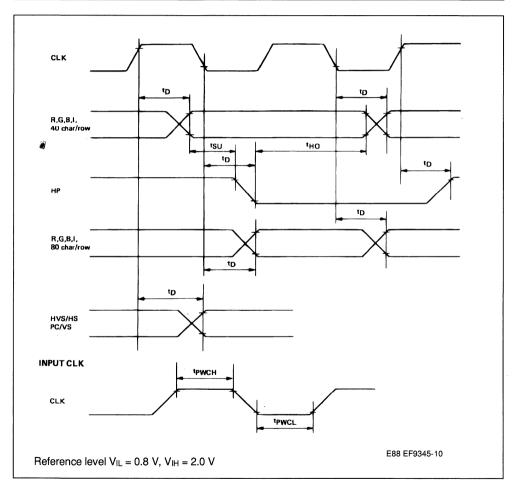

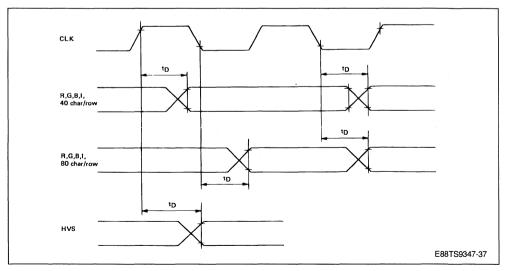

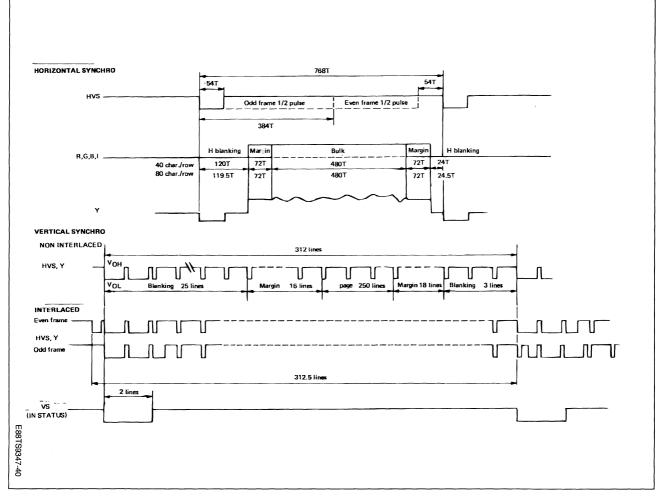

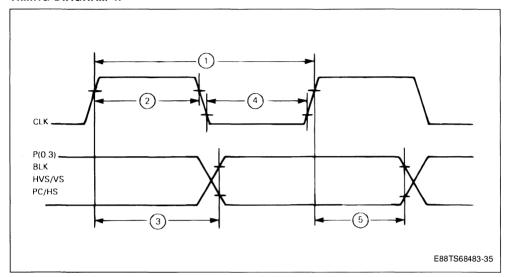

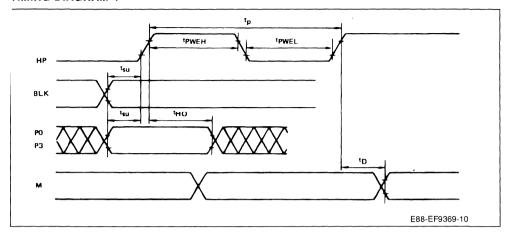

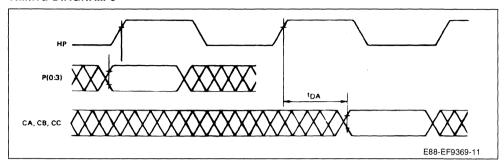

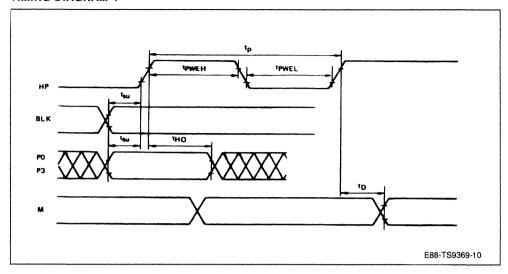

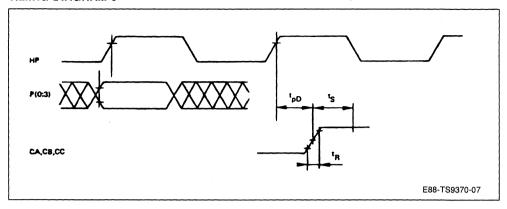

#### VIDEO INTERFACE R, G, B, I, HP, HVS / HS, PC / VS

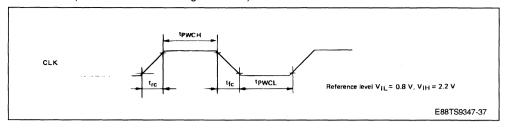

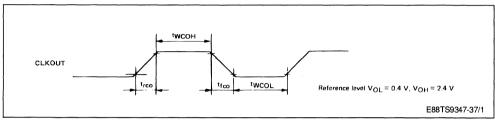

$V_{CC}$  = 5.0 V ± 5 %,  $T_A$  = 0° to + 70 °C, CLK Duty Cycle = 50 %,  $C_L$  = 50 pF Reference Levels :  $V_{IL}$  = 0.8 V and  $V_{IH}$  = 2.2 V on CLK input.  $V_{OL}$  = 0.4 V and  $V_{OH}$  = 2.4 V on all outputs.

| Symbol          | Parameter                    | Min. | Тур. | Max. | Unit |

|-----------------|------------------------------|------|------|------|------|

| tsu             | Setup Time R, G, B, I to HP  | 10   | _    | _    | ns   |

| t <sub>HO</sub> | Hold Time R, G, B, I from HP | 50   | _    | -    | ns   |

| t <sub>D</sub>  | Output Delay from CLK Edge   | _    | -    | 60   | ns   |

| tpwch           | CLK High Pulse Width         | 30   |      |      | n,s  |

| tpwcL           | CLK Low Pulse Width          | 30   |      |      | ns   |

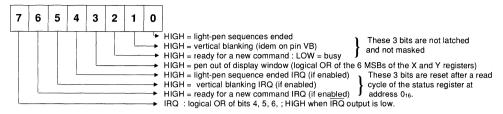

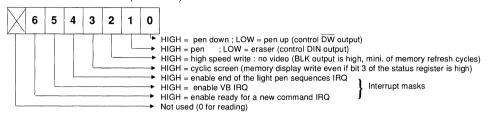

#### **EF 9345 PIN DESCRIPTION**

All the input/output pins are TTL compatible.

#### MICROPROCESSOR INTERFACE

| Name     | Pin<br>Type | N°                 | Function                                                                                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|-------------|--------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD (0:7) | I/O         | 17 – 19<br>21 – 25 | Multiplexed<br>Address/Data<br>Bus                                                                        | These 8 bidirectional pins provide`communication with the microprocessor system bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

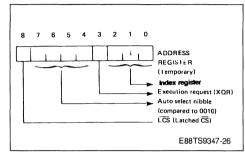

| AS       | I           | 14                 | Address<br>Strobe                                                                                         | The falling edge of this control signal latches the address on the AD (0:7) lines, the state of the Data Strobe (DS) and Chip Select (CS) into the chip.                                                                                                                                                                                                                                                                                                                                                                                                       |

| DS       | _           | 15                 | Data Strobe                                                                                               | When this input is strobed high by AS, the output buffers are selected while DS is low for a read cycle (R/ $\overline{W}$ = 1). In write cycle, data present on AD (0:7) lines are strobed by R/ $\overline{W}$ low (see timing diagram 2). When this input is strobed low by AS, R/ $\overline{W}$ gives the direction of data transfer on AD (0:7) bus. $\overline{DS}$ high strobes the data to be written during a write cycle (R/ $\overline{W}$ = 0) or enables the output buffers during a read cycle (R/ $\overline{W}$ = 1). (see timing diagram 1). |

| R/W      | Î           | 16                 | Read/Write This ipnut determines whether the internal registers get or read. A write is active low ("0"). |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CS       |             | 26                 | Chip Select                                                                                               | The EF9345 is selected when this input is strobed low by AS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

#### MEMORY INTERFACE

| Name      | Pin<br>Type | N°      | Function                           | Description                                                                                                                                              |  |  |  |  |

|-----------|-------------|---------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| ADM(0:7)  | I/O         | 40 – 43 | Multiplexed<br>Address/Data<br>Bus | Lower 8 bits of memory address appear on the bus when $\overline{\text{ASM}}$ is high. It then becomes the data bus when $\overline{\text{ASM}}$ is low. |  |  |  |  |

| AM (8:13) | 0           | 32 – 27 | Memory<br>Address Bus              | These 6 pins provide the high order bits of the memory address.                                                                                          |  |  |  |  |

| ŌĒ        | 0           | 2       | Output Enable                      | When low, this output selects the memory data output buffers.                                                                                            |  |  |  |  |

| WE        | 0           | 3       | Write Enable                       | This output determines whether the memory gets read or written. A write is active low ("0").                                                             |  |  |  |  |

| ASM       | 0           | 4       | Memory<br>Address<br>Strobe        | This signal cycles continuously. Address can be latched on its falling edge.                                                                             |  |  |  |  |

#### OTHER PINS

| Name | Pin<br>Type | N° | Function     | Description                                                            |

|------|-------------|----|--------------|------------------------------------------------------------------------|

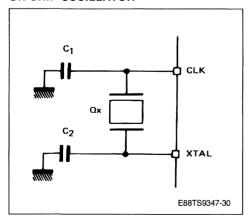

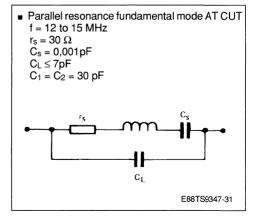

| CLK  | I           | 12 | Clock Input  | External TTL clock Input. (nominal value : 12 MHz, duty cycle : 50 %). |

| Vss  | S           | 1  | Power Supply | Ground.                                                                |

| Vcc  | S           | 20 | Power Supply | + 5 V                                                                  |

#### VIDEO INTERFACE

| Name    | Pin<br>Type | N° | Function                               | Description                                                                                                                                                                   |

|---------|-------------|----|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R       | 0           | 7  | Red                                    | These outputs deliver the video signal. They are low during the                                                                                                               |

| G       | 0           | 8  | Green                                  | vertical and horizontal blanking intervals.                                                                                                                                   |

| В       | 0           | 9  | Blue                                   |                                                                                                                                                                               |

| _       | 0           | 10 | Insert                                 | This active high output allows to insert R:G:B:in an external video signal for captioning purposes, for example. It can also be used as a general purpose attribute or color. |

| HVS/HS  | 0           | 5  | Sync. Out                              | This output delivers either the composite synchro (bit $TGS_4 = 1$ ) or the horizontal synchro signal (bit $TGS_4 = 0$ ).                                                     |

| PC/VS   | 0           | 6  | Phase<br>Comparator /<br>Vertical Sync | When $TGS_4 = 1$ , this signal is the phase comparator output.<br>When $TGS_4 = 0$ , this output delivers the vertical synchro signal.                                        |

| SYNC IN | I           | 13 | Synchro In                             | This input allows vertical and/or horizontal synchronizing the EF9345 on an external signal. It must be grounded if not used.                                                 |

| HP      | 0           | 11 | Video Clock                            | This output delivers a 4 MHz clock phased with the R, G, B, I signals                                                                                                         |

#### GENERAL DESCRIPTION

The EF9345 is a low cost, semigraphic, CRT controller.

It is optimized for use with a low cost, monochrome or color TV type CRT (64  $\mu s$  per line, 50 or 60 Hz refresh frequency).

The EF9345 displays up to 25 rows of 40 characters or 25 rows of 80 characters.

The on-chip character generator provides a 128 standard, 5 x 7, character set and standard semi-graphic sets.

More user definable (8  $\times$  10) alphanumeric or semigraphic sets may be mapped in the 16 K  $\times$  8 private memory addressing space.

These user definable sets are available only in 40 characters per row format.

#### MICROPROCESSOR INTERFACE.

The EF9345 provides an 8-bit, address/data multiplexed, microprocessor interface.

It is directly compatible with popular (6801, 8048, 8051, 8035...) microprocessors.

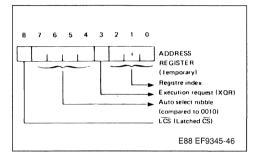

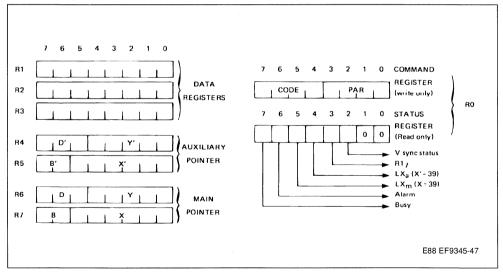

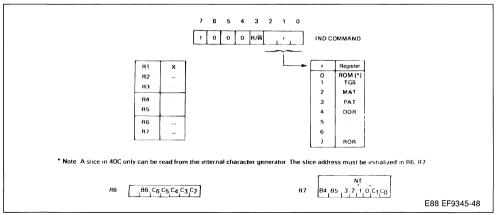

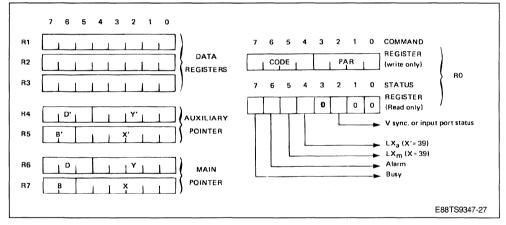

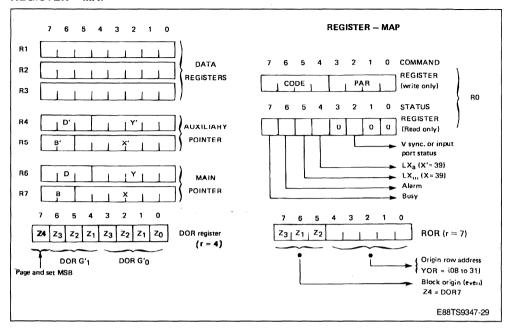

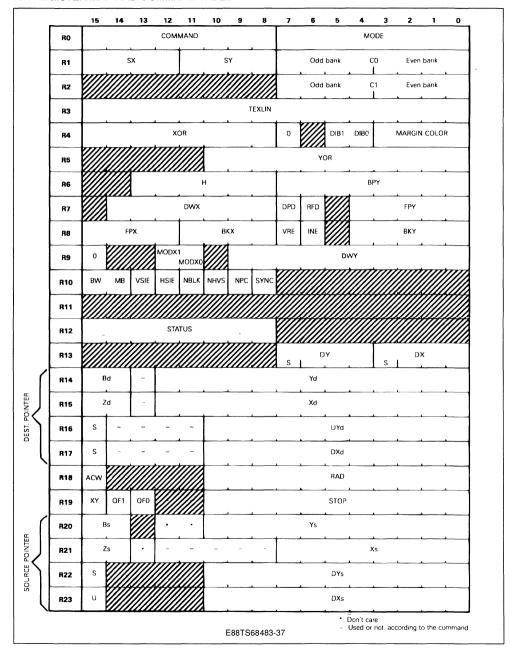

#### REGISTERS.

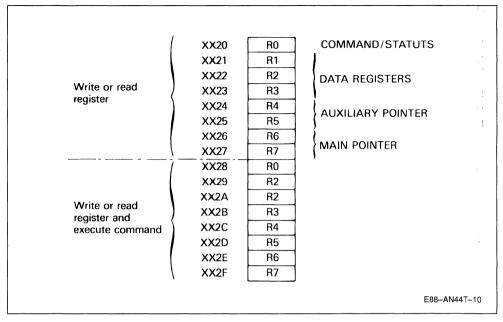

The microprocessor directly accesses 8 registers:

- R0 : Command/status register

- R1, R2, R3 : Data registers

- R4, R5 : Each of these register pairs points R6, R7 into the private memory.

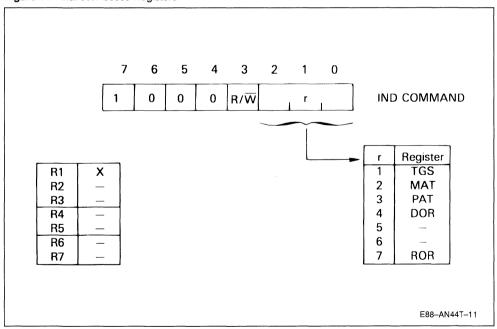

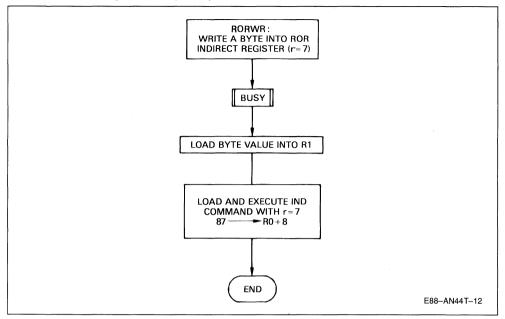

Through these registers, the microprocessors indirectly accesses the private memory and 5 more registers:

- ROR, DOR: Base address of displayed page memory and of used external character generators.

- PAT, MAT, TGS: Used to select the page attributes and format, and to program the timing generator option.

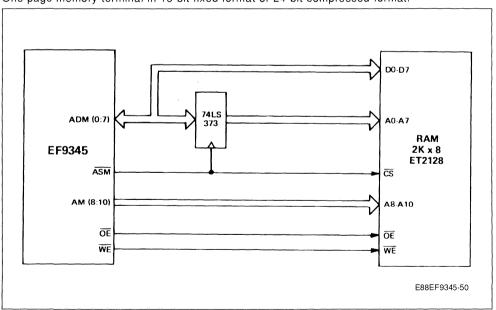

#### PRIVATE MEMORY

The user may partition the 16 K x 8 private memory addressing space between:

- pages of character codes (2 K x 8 or 3 K x 8),

- · external character generators,

- · general purpose user area.

Many types of memory components are suitable:

- ROM, DRAM or SRAM,

- 2 K x 8, 8 K x 8, 16 K x 4 organizations,

- Modest 500 ns cycle time and 250 ns access time is required.

### 40 CHARACTERS PER ROW: CHARACTER CODE FORMATS AND ATTRIBUTES.

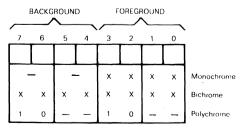

Once the 40 characters per row format has been selected, one character code format out of three must be chosen:

- 24-bit fixed format :

- All the attributes are provided in parallel.

- 8/24-bit compressed format :

- All the attributes are latched.

- 16-bit fixed format :

- Some parallel attributes, other are latched.

The 16-bit fixed format is compatible with EF9340/41 CRT controller.

12/50

#### Character attributes provided:

- Background and foreground color (3 bits each),

- Double height, double width,

- Blinking,

- Reverse,

- Underlining,

- Conceal.

- Insert.

- Accentuation of lower case characters

- 3 x 100 user definable character generator in memory

- 8 x 100 semi-graphic quadrichrome characters.

## 80 CHARACTERS PER ROW FORMAT : CHARACTER CODE FORMAT AND ATTRIBUTES.

Two character code formats are provided:

- Long (12 bits) with 4 parallel attributes :

- \_ Blinking,

- Underlining,

- Reverse,

- Color select.

- · Short (8 bits) : no attributes.

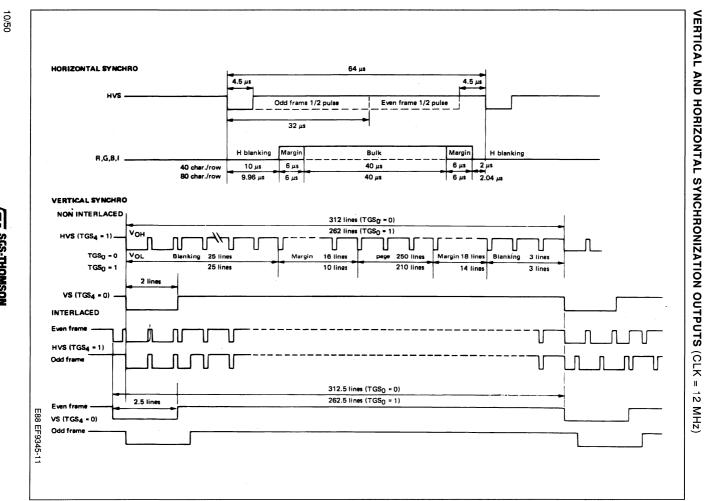

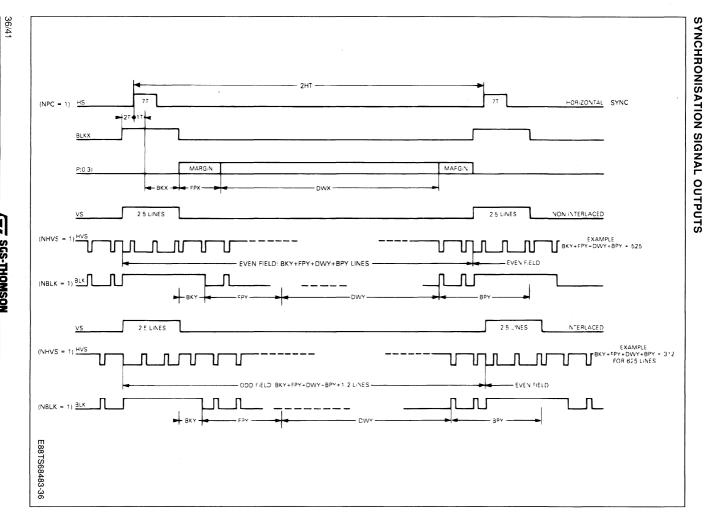

#### TIMING GENERATOR.

The whole timing is derived from a 12 MHz main clock input.

The RGB outputs are shifted at 8 MHz for the 40 character/row format and at 12 MHz for the 80 character/row.

Besides, the user may select:

- 50 Hz or 60 Hz vertical sync. frequency,

- · Interlaced or not.

- Separated or composite vertical and horizontal sync. outputs.

Furthermore, a composite sync. input allows, when it is required:

- An on-chip vertical resynchronization.

- An on-chip crude horizontal resynchronization,

- An off-chip high performance horizontal resynchronization by use of a simple external VCXO controlled by the on-chip phase comparator.

#### **MEMORY ORGANIZATION**

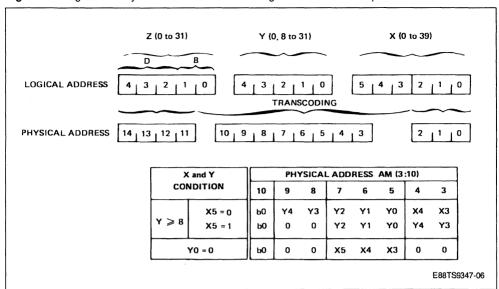

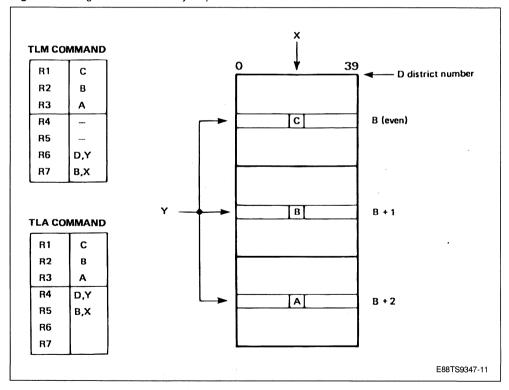

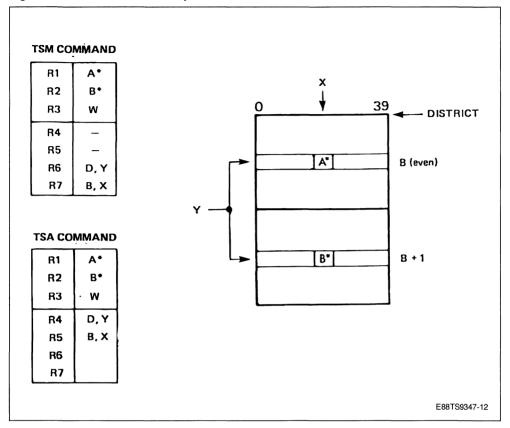

#### LOGICAL AND PHYSICAL ADDRESSING.

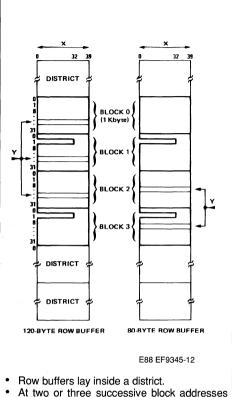

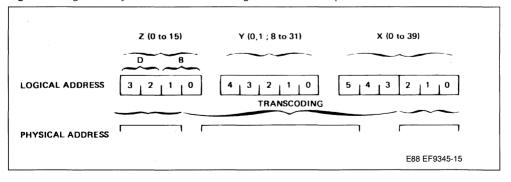

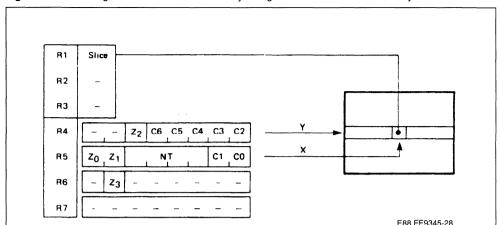

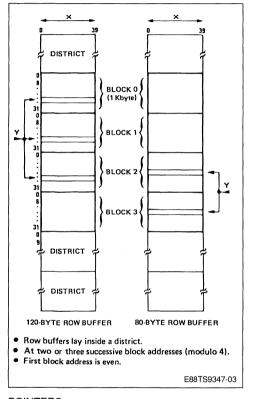

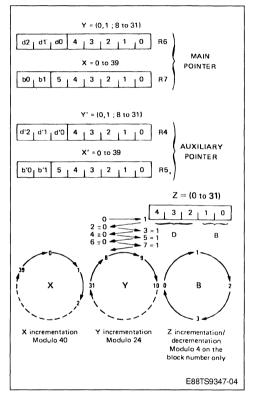

The physical 16-Kbyte addressing space is logically partitioned by EF9345 into 40-byte **buffers** (figure 1). More precisely, a logical address is given by an X, Y, Z triplet where:

- X = (0 to 39) points to a byte inside a buffer,

- Y = (0, 1; 8 to 31) points to a buffer inside a 1 Kbyte block,

- Z = (0 to 15) points to a **block**.

Obviously, 1 K =  $2^{10}$  = 1024 cannot be exactly divided by 40. Consequently, any block holds 25 full buffers and a 24-byte remainder. Provided that the physical memory is a multiple of 2 Kbytes, the remainders are paired in such a way as to make available :

- a full buffer (Y = 1) in each even block,

- a partial buffer (Y = 1; X = 32 to 39) in each odd block.

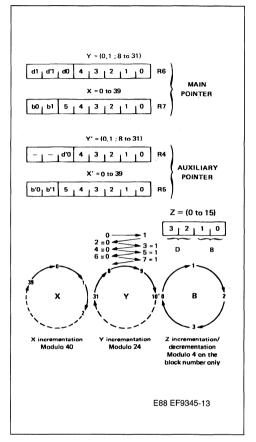

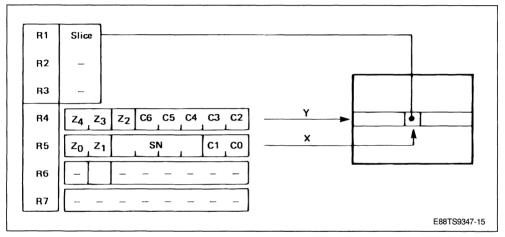

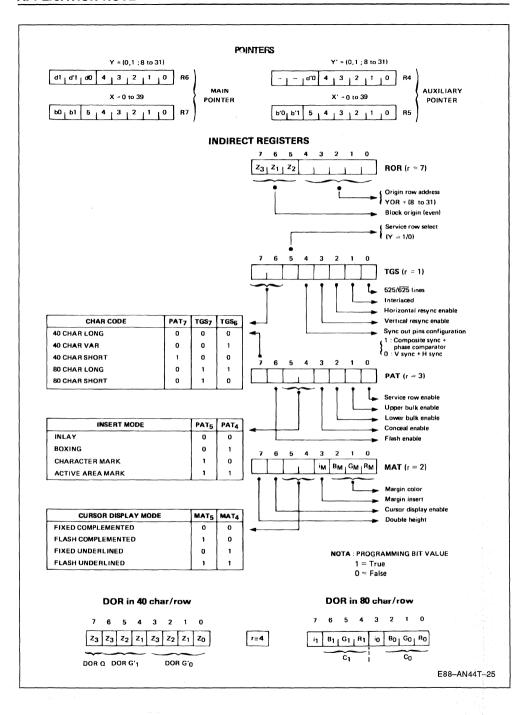

#### POINTERS.

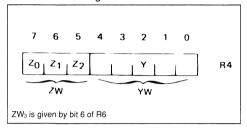

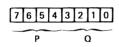

Each X, Y and Z component of a logical address is binary encoded and packed in two 8-bit registers. Such a register pair is a pointer (figure 2). EF9345 contains two pointers:

- R4, R5 : auxiliary pointer,

- R6, R7: main pointer.

R5 and R7 have the same format. Each one holds an X component and the two LSB's of a Z component. This packing induces a partitioning of Z in 4 **districts** of 4 blocks each.

R5, R7 points to a block number in a district. R4 and R6 have a slightly different format: Each one holds a Y component and the LSB of the district number. But R6 holds both district MSB.

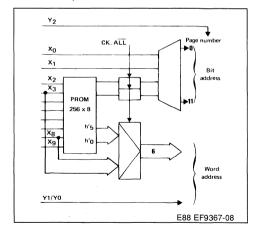

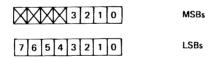

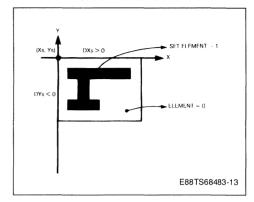

Figure 4 gives the logical to physical address transcoding scheme performed on chip.

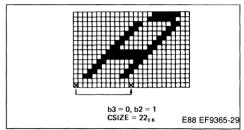

Figure 1: Memory Row Buffer.

- At two or three successive block addresses (modulo 4).

- · First block address is even.

#### DATA STRUCTURES IN MEMORY.

A **page** is a data structure displayable on the screen up to 25 rows of characters. According to the character code format, each row on the screen is associated with 2 (or 3) 40-byte buffers. This set of 2 (or 3) buffers constitutes a row **buffer** (figure 1). The buffers belonging to a row buffer must meet the following requirements:

- they have the same Y address,

- they have the same district number,

- they lie at 2 (or 3) successive (modulo 4) block addresses in their common district.

Consequently, a row buffer is defined by its first buffer address and its format.

A page is a set of successive row buffers:

- with the same format.

- · with the same district number.

Figure 2: Pointer Auto Incrementation.

- with the same block address of first buffer. This block address must be even.

- lying at successive (modulo 24) Y addresses.

Consequently, a page should not cross a district boundary. General purpose memory area may be used but should respect the buffer or row buffer structure. See figure 2 for pointer incrementation implied by these data structures.

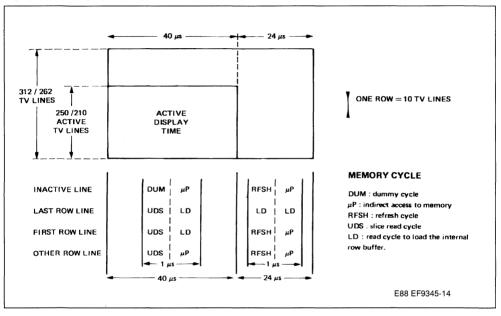

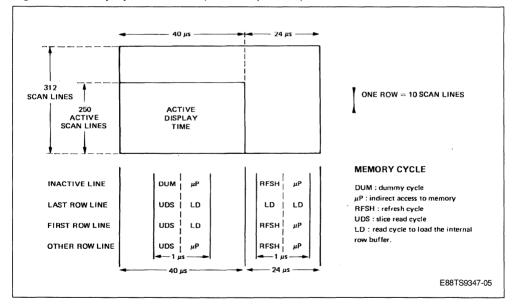

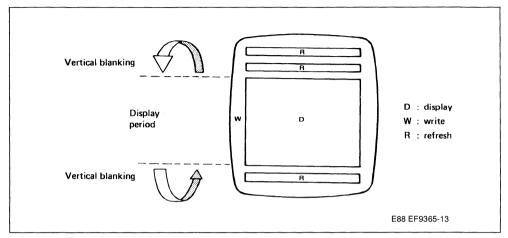

#### MEMORY TIME SHARING (see figure 3).

The memory interface provides a 500 ns cycle time. That is to say a 2 Mbyte/s memory bandwidth. This bandwidth is shared between:

- reading a row buffer from memory to load the internal row buffer (up to 120 bytes once each row),

- reading user defined characters slices from memory (1 byte each μs),

- indirect microprocessor read or write operation,

- refresh cycles to allow DRAM use, with no overhead.

A fixed allocation scheme implements the sharing. Notes on Figure 3.

- Dummy cycles are read cycles at dummy addresses.

- RFSH cycles are read cycles performed by an 8bit auto-incrementing counter. Low order address byte ADM (0:7) cycles through its 256 states in less than 1 ms.

Figure 3: Memory Cycle Allocation.

The microprocessor may indirectly access the memory once every μs, except during the first and the last line of a row, when the internal buffer must be reloaded.

During these lines, no microprocessor access is provided for 104  $\mu s$ ; this hold too when no user defined character slices are addressed.

Figure 4: Logical to Physical Address Transcoding Performed On-chip.

| X and Y   |                  |                  | PHYSICAL ADDRESS AM (3:10) |         |         |          |          |          |          |          |

|-----------|------------------|------------------|----------------------------|---------|---------|----------|----------|----------|----------|----------|

| Condition |                  |                  | 10                         | 9       | 8       | 7        | 6        | 5        | 4        | 3        |

| Y ≥ 8     | X5 = 0<br>X5 = 1 |                  | b0<br>b0                   | Y4<br>0 | Y3<br>0 | Y2<br>Y2 | Y1<br>Y1 | Y0<br>Y0 | X4<br>Y4 | X3<br>Y3 |

|           | Y0               | = 0              | b0                         | 0       | 0       | X5       | X4       | ХЗ       | 0        | 0        |

| Y < 8     | Y0 = 1           | b0 = 0<br>b0 = 1 | X3<br>I                    | 0<br>0  | 0       | l<br>I   | X5<br>X5 | X4<br>X4 | 0<br>0   | 0        |

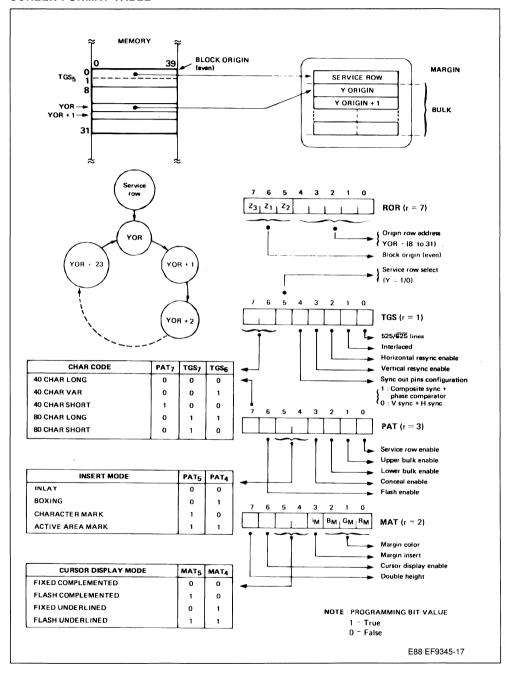

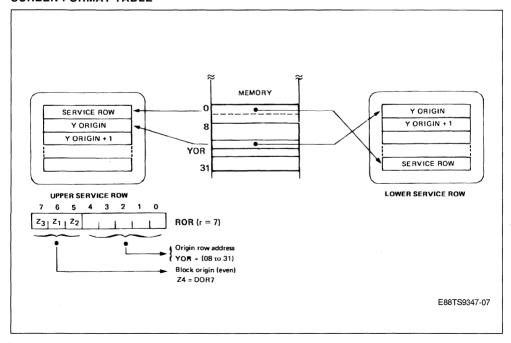

#### SCREEN FORMAT AND ATTRIBUTES

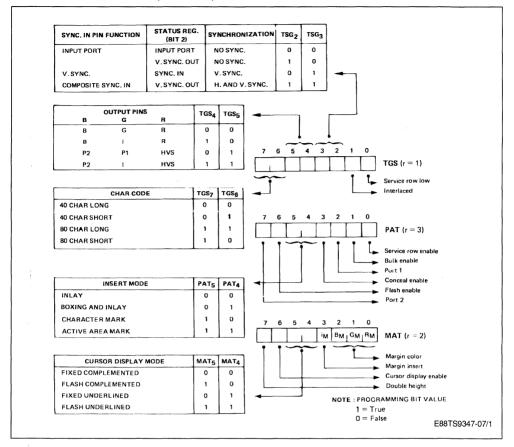

The screen format and attributes are programmed through 5 indirectly accessible registers: ROR, TGS, PAT, MAT and DOR. IND command allows accessing these registers. TGS is also used to select the timing generator options (see Screen Format Table).

## ROW AND CHARACTER CODE FORMAT PAT7: TGS(6:7).

Two row formats and 5 character code formats are available but cannot be mixed in a given screen. DOR register interpretation is completely row format dependent and is discussed in the corresponding 40 char/row and 80 char/row section.

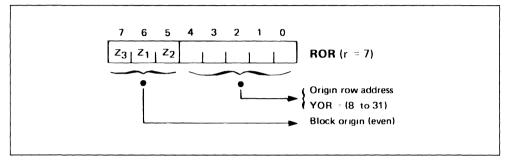

SCREEN PARTITION - PAGE POINTER ROR (see top of the Screen Format Table).

The screen is partitionned into 3 areas:

- · the margin.

- the service row.

- · the bulk of remaining rows.

MAT<sub>(0:3)</sub> declares the color of the margin and the value I<sub>M</sub> of its insert attribute.

ROR register points to the page to be displayed and gives the 3 MSB's of the Z address:  $Z_0 = 0$  implicitly; the page block address must be even. YOR gives the first row buffers to be displayed at the top of the bulk area. The next row buffers to be displayed are fetched sequentially by incrementing the Y address (modulo 24). This address never gets out of the origin block. Incrementation of YOR by the microprocessor yields a roll up.

#### SERVICE ROW: TGS5 - PAT0.

The service row is displayed for 10 TV lines on top of the screen and does not roll. Following TGS<sub>5</sub>, it is fetched from the origin block at either Y=0 or Y=1. The Y=1 is a partial row buffer. It can be used only with variable 40 char./row and an 8 byte attribute file. The service row may be disabled by PAT<sub>0</sub> = 0; it is then displayed as a margin extension.

BULK: TGS<sub>0</sub>; PAT<sub>(1:2)</sub>; MAT<sub>7</sub>.

It is displayed after the service row for 200 or 240 TV lines according to  $TGS_0$ . Each row buffer is usually displayed for 10 TV lines. However,  $MAT_7 = 1$  doubles this figure. Then every character appears in double height (double height characters are quadrupled).

$PAT_1 = 0$  and/or  $PAT_2 = 0$  disables respectively the upper 120 lines and/or the lower 80/120 lines of the bulk.

When disabled, the corresponding TV lines are displayed as a margin extension.

#### CURSOR MAT(4:6)

To be displayed with the cursor attributes, a character must be pointed by the main pointer (R6, R7) and MAT $_6$  must be set. The cursor attributes are given by MAT $_{(4:5)}$ :

Complementation: the R, G and B of each pixel is logically negated.

$R, G, B \rightarrow \overline{R}, \overline{G}, \overline{B}$

- Underline: the underline attribute of this character is negated.

- Flash: the character is periodically displayed with, then without, its cursor attributes (50 % / 50 %; ≈ 1 Hz).

## FLASH ENABLE (PAT<sub>6</sub>) - CONCEAL ENABLE (PAT<sub>3</sub>).

Any character flashing attribute is a "don't care" when  $PAT_6 = 0$ . When  $PAT_6 = 1$ , a character flashes if its flashing attribute is set. It is then periodically displayed as a space (50 % / 50 %;  $\approx$  0.5 Hz).

PAT<sub>3</sub> is a "don't care" for 80 char./row formats. When any 40 char./row format is in use :

- if PAT<sub>3</sub> = 0, the conceal attribute of any character is a don't care.

- if PAT<sub>3</sub> = 1, the conceal attribute of each character is interpreted: a concealed character appears as a space on the screen.

#### INSERT MODES: PAT(4:5).

During retrace, margin and extended margin periods, the I output pin delivers the value of the insert margin attribute.

$I = I_M = MAT_4$ .

During active line period, the I output state is controlled by the Insert Mode and i, the insert attribute of each character. The I output pin may have several uses: (see figure below):

As a margin/active area signal in the active area mark mode.

As a character per character marker signal in the character mark mode.

As a video mixing signal in the two remaining modes, provided that the EF9345 has been vertically and horizontally synchronized with an external video source: the I pin allows mixing RGB outputs (I = 1) and the external video signal (I = 0). This mixing can be achieve by switching or ORing. It may occur for the complete character window (Boxing Mode) or only for the foreground pixels (Inlay Mode).

#### VIDEO OUTPUTS DURING ACTIVE PERIODS

| Insert Mode      |   | Char. Level        |        | Outputs     |  |  |

|------------------|---|--------------------|--------|-------------|--|--|

| misert mode      | i | Pixels (1)         | ì      | R, G, B (2) |  |  |

| Active Area Mark | - | _                  | 1      | Х           |  |  |

| Character Mark   | 0 |                    | 0      | X<br>X      |  |  |

| Boxing           | 0 | <u>-</u><br>-      | 0      | BLACK<br>X  |  |  |

|                  | 0 | _                  | 0      | BLACK       |  |  |

| Inlay            | 1 | BACKGND<br>FOREGND | 0<br>1 | BLACK<br>X  |  |  |

#### NOTES :

#### (1) PIXEL TYPE

- : Don' t care

FOREGND = A foreground pixel is :

- · Any pixel of a quadrichrome character,

- A Pixel of a bichrome character generated from a "1" in the character generator cell.

#### (2) RGB OUTPUTS

X : Not affected.

BLACK: forced to low level.

#### TIMING GENERATOR OPTIONS:TGS (0:4)

TGS<sub>(0:1)</sub> select the number of lines per frame :

| TGS₁ | TGS <sub>0</sub> | LINES |                |

|------|------------------|-------|----------------|

| 0    | 0                | 312   | NON INTERLACED |

| 0    | 1                | 262   | NON INTERLACED |

| 1    | 0                | 312.5 | INTERLACED     |

| 1    | 1                | 262.5 | INTERLACED     |

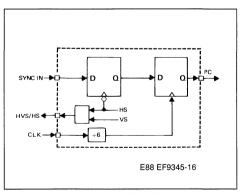

The composite incoming SYNC IN signal is separated into 2 internal signals :

- Vertical Synchronization In (VSI),

- Horizontal Synchronization In (HSI).

TGS<sub>3</sub> enables VSI to reset the internal line count. SYNC IN input is sampled at the beginning of the active area of each line. When the sample transits from 1 to 0, the line count is reset at the end of the current line.

TGS<sub>2</sub> enables HSI to control an internal digital phase lock loop. HSI and on-chip generated HS Out are considered as in phase if their leading edges match at ±1 clock period.

When they are out of phase, the line period is lengthened by 1 clock period (  $\approx$  80 ns).

TGS<sub>4</sub> controls the SYNC OUT pins configuration :

| TGS₄ | HVS / HS       | PC / VS    |  |  |

|------|----------------|------------|--|--|

| 1    | Composite Sync | PC         |  |  |

| 0    | H Sync Out     | V Sync Out |  |  |

PC is the output of the on-chip phase comparator.

An external VCXO allows a smoother horizontal phase lock than the internal scheme.

#### SCREEN FORMAT TABLE

#### **40 CHAR/ROW CHARACTER CODES**

To display pages in 40 character per row format, one out of three character code formats must be selected:

- Fixed long (24 bits) code : all parallel attributes.

- Fixed short (16 bits) code: mix of parallel and latched attributes.

- Variable (8/24 bits) code: all latched attributes.

Fixed short and variable codes are translated into fixed long codes by EF9345 during the internal row buffer loading process. The choice of the character code format is obviously a display flexibility/memory size trade off, left up to the user.

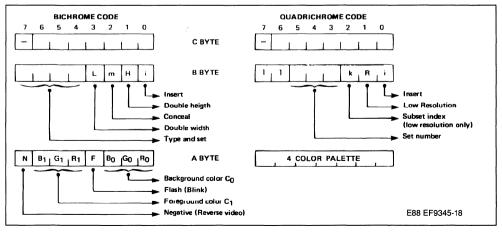

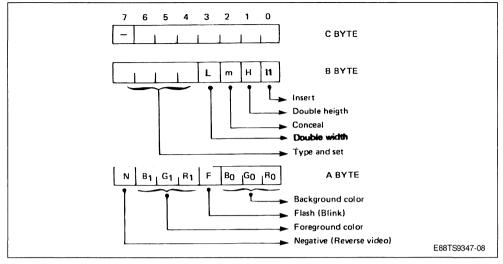

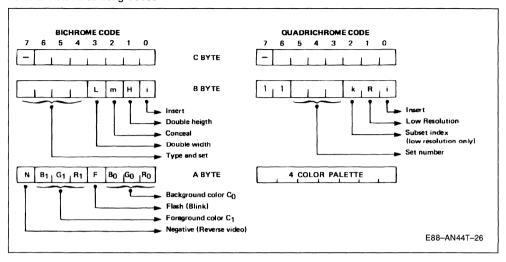

#### FIXED LONG CODES.

This is the basic 40 char./row code. Each 8 pixels x 10 lines character window, on the screen is associated with a 3-byte code in memory, namely the C, B and A bytes (figure 5). A row on the screen is associated with a 120 byte row buffer in memory.

#### 3-BYTE CODE STRUCTURE.

- C7 is a don't care. Up to 128 characters may be addressed in each set. Each user definable set holds only 100 characters: C byte value ranges from 00 to 03 and 20 to 7F (hexa).

- B(4:7) give the type and set number of the character.

- All the bichrome characters have the same attributes except that alphanumerics may be underlined, semi-graphics cannot. Accentuated alphanumerics allow orthogonal accentuating of any one of the 32 lower case ROM characters with any of 8 accents (see figure 19).

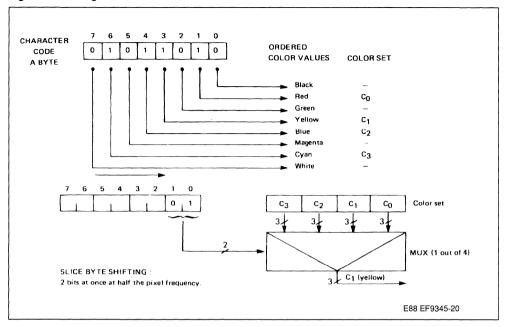

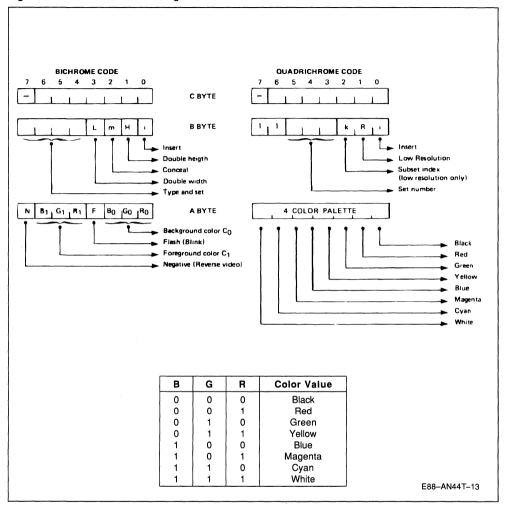

4. Bichrome and quadrichrome characters use two different coloring schemes.

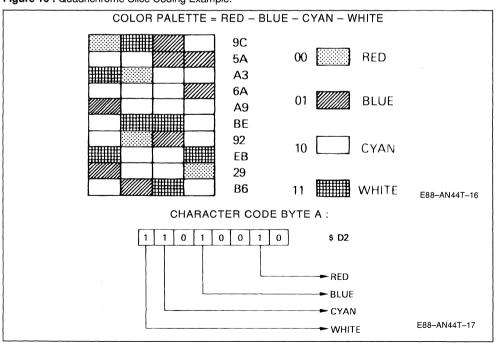

For bichrome characters, character code byte A defines a two color set by giving directly two color values (figure 6). The negative attribute exchanges the two values. Each bit of the slice byte selects one color value out of two.

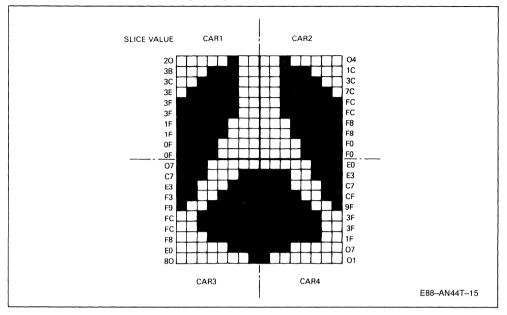

The "A" byte in a quadrichrome character code defines an ordered 4 color set (figure 7). When more than 4 bits are set, higher ranking bits are ignored. When less than 4 bits are set, the color set is completed with implicit "white" value. The slice byte is shifted 2 bits at once at half the dot frequency ( $\approx$  4 MHz).

Each bit pair designates one color out of the 4 color sets.

Quadrichrome characters allow displaying up to 4 different colors (instead of 2) in any 8 x 10 window at the penalty of an halved horizontal resolution.

By programming the R attribute in byte B, one may chose to keep the full vertical resolution (1 slice per line) or to halve it (each slice is repeated twice). In any case, it is possible to change the color set freely from window to window and to mix freely all the character types. So, fairly complex pictures may be displayed at low memory cost.

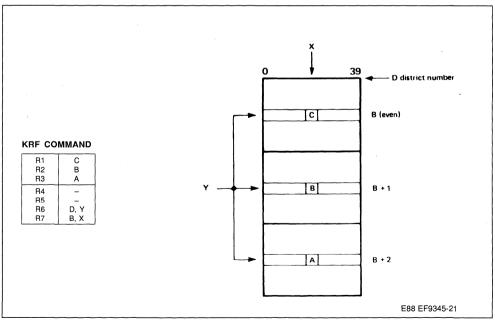

#### HANDLING LONG CODES.

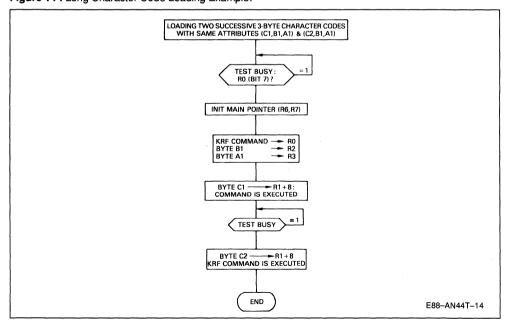

The KRF command allows an easy X, Y random access or an X sequential access to/from the microprocessor from/to a memory row buffer (figure 8).

Figure 5: (continued).

|   | Type and Set<br>Code: B(4:7) |     |               | Number of Character<br>Per Set               | Set<br>Name                            | Set<br>Type | Set<br>Type   |                |

|---|------------------------------|-----|---------------|----------------------------------------------|----------------------------------------|-------------|---------------|----------------|

| 7 | 6                            | 5   | 4             | <b>C</b> (0:6)                               |                                        |             |               |                |

|   | 0                            | 1   | 0             | 128 Standard Mosaïcs<br>32 Strokes           | G <sub>10</sub><br>G <sub>11</sub>     | SEMI-GR.    |               |                |

| 0 | 0                            | 0   | U             | 128 Alphanumerics                            | G <sub>0</sub> .                       |             | В             |                |

|   | 1                            | 0 1 | N D E R L - N | Accentuated Lower Case Alpha                 | G <sub>20</sub><br>G <sub>21</sub>     | ALPHA       | I C H R O M E | ON-CHIP<br>ROM |

|   | 0                            | 0   | Е             | 100 Alpha UDS                                | G'₀                                    |             | -             |                |

| 1 | 0                            | 1   | 0<br>1        | 100 Semi-graphic UDS<br>100 Semi-graphic UDS | G' <sub>10</sub><br>G' <sub>11</sub>   | SEMI-GR.    |               | EXTERNAL       |

|   | 1                            | х   | Х             | 8 Sets of 100  Quadrichrome Character        | Q <sub>0</sub><br>to<br>Q <sub>7</sub> | QUADRICH    | ROME          | MEMORY         |

Note: Programming bit value: 1 = True; 0 = False.

Figure 6 : Coloring with Bichrome Characters.

| В     | G     | R   | Color Value      | 7                               |

|-------|-------|-----|------------------|---------------------------------|

|       |       |     |                  | 4                               |

| 0     | 0     | 0   | Black            |                                 |

| 0     | 0     | 1   | Red              | 7 6 5 4 3 2 1 0                 |

| 0     | 1     | 0   | Green            | CHARACTER N B1 G1 R1 F B0 G0 R0 |

| 0     | 1     | 1   | Yellow           | CODE                            |

| 1     | 0     | 0   | Blue             | A BYTE                          |

| 1     | 0     | 1   | Magenta          |                                 |

| 1     | 1     | 0   | Cyan             | 3 3                             |

| 1     | 1     | 1 _ | White            |                                 |

|       |       |     |                  |                                 |

|       |       |     |                  | N = 1 Exchanges values          |

|       |       |     |                  | C <sub>1</sub>                  |

|       |       |     |                  | Background                      |

|       |       |     |                  | Foreground 3 Background color   |

|       |       |     | SHIFTED SLICE BY |                                 |

|       |       |     | (LSB first)      |                                 |

|       |       |     |                  |                                 |

|       |       | 7 ( | 5 5 4 3 2        | 1 0 MUX                         |

|       |       | 0   | 1 0 1 0 0        | 1 0                             |

|       |       |     | • •              |                                 |

| Foreg | round | •   |                  | 3 Pixel color R,G,B             |

|       |       |     |                  |                                 |

|       |       |     |                  |                                 |

Figure 7: Coloring with Quadrichrome Characters.

Figure 8: Fixed Long Codes in Memory 120 Byte Row Buffer.

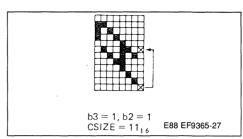

#### VARIABLE CODES

In many cases, successive characters on screen belong to the same character set and have the same attributes. Variable codes achieve memory saving by storing B and A bytes only when it is required by exploiting the C7 bit.

C7 = 1 This is a long 3-byte code.

Character set and attribute values are completely redefined by B and A bytes.

C7 = 0 This is a short 1-byte code.

Character set and attributes value are identical to the previous code.

A further saving comes from the fact that an accentuated alphabetic character is, more often than not, followed by a not accentuated alphabetic character.

So,  $G_{20}$  or  $G_{21}$  sets are processed as one-shot escape with return to  $G_0$ . For normal operation, variable codes should obey the following rules:

- the first character code of any row (X = 0) should be long.

- a character code may be short when it has the same attributes as the previous character code and belongs to the same set.

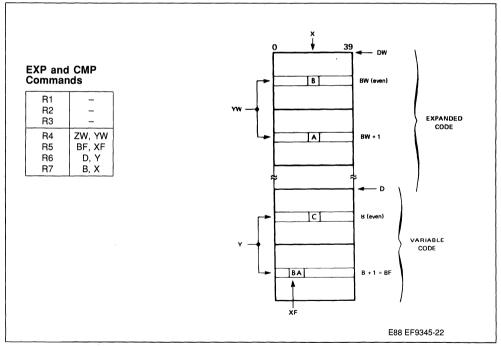

Figure 9: Expansion / Compression Move.

#### However:

- any code belonging to G<sub>20</sub> or G<sub>21</sub> must be long and must be repeated if the character is double width,

- a code belonging to G<sub>0</sub> following a G<sub>20</sub> or G<sub>21</sub> code may be short.

#### HANDLING THE VARIABLE CODES.

During the display process, a row of variable code should be laid in an 80/120 byte row buffer. The first buffer holds the C bytes. The second buffer holds the B, A file providing up to 20 long codes per row (figure 10). In the exceptionnal case when this is not enough, the second buffer overflows in the third one. Every code may then be long. Variable codes can almost always achieve a memory saving over long fixed codes and can never be worse.

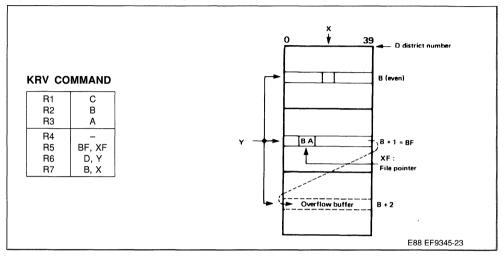

The KRV command gives a very easy sequential access to/from a row buffer from/to the microprocessor. This command automatically updates the C byte and the B, A file pointers (the last one when C7 is set).

Random access to a variable code is obviously not as easy. The EXP, KRE are CMP commands are designed to facilitate this task (figure 9).

The EXP command translates a full row of variable codes into a row of expanded codes. Expanded codes are generally not displayable but very similar to the long codes.

Figure 10: Variable Codes in Memory.

KRE gives a random access to an expanded code and makes it appear as a regular long code.

The CMP command translates a full row of expanded code into a row of variable codes and minimizes the file size in the process.

These commands use a buffer pair as working area.

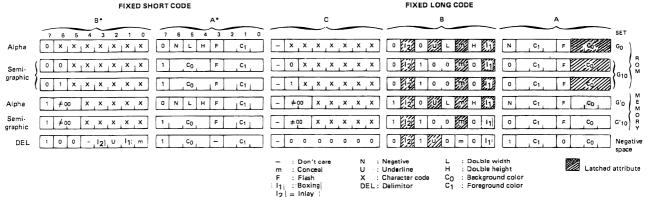

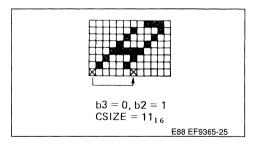

#### FIXED SHORT CODES.

These fixed 16-bit codes are compatible with EF9340/41 display controllers. They achieve memory saving by another way. They may be easier to handle than variable codes. The penalty is in lesser display capabilities:

- accentuated character sets are no longer available: accentuated characters must be individually provided by the character generators.

- G'<sub>11</sub> and quadrichrome sets cannot be reached,

- some attributes are latched and can be changed only while displaying a space (delimitor code).

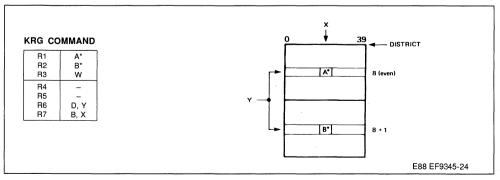

The KRG command allows an easy access from/to an 80-byte row buffer in memory to/from the micro-processor (figure 11). Figure 12 gives the fixed short to fixed long translation process which occurs for each row - while loading the internal row buffer - before display.

Figure 11: Fixed Short Codes in Memory 80 Byte Row Buffer.

Figure

12

Fixed

Short Code to

Fixed Long Code

Translation

### Notes:

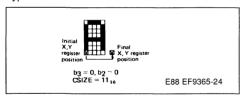

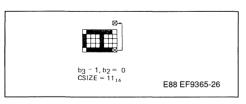

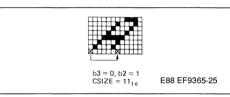

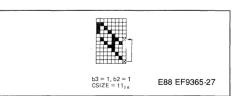

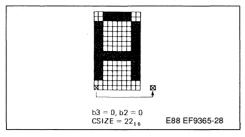

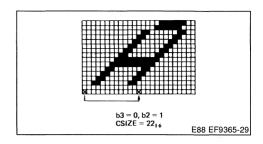

E88 EF9345-25

The translation process operates through 3 elementary operations:

- · Fleid-to-fleid: a character code or an attribute value (i.e : Co, flashing) is directly loaded from short to long code.

- Field-to-constant: the decoding of a short code forces the value of the equivalent long code attribute. For example, semigraphic short characters forces normal size (H = 0, L = 0) attributes.

- · Latched attributes at the beginning of each row, these attributes are reset (no underline, not concealed, black background). Then, they keep their current value until modified by either a field to field or field to constant operation.

2. EF9340 41 Compatibility.

It is binary code compatible with few exceptions:

- · Flashing attribute is negated,

- A7 is negated in delimitors.

It is also display compatible with 2 exceptions concerning the underling :

- An alphanumeric belonging to G'o may be underlined.

- Any alphanumeric following a semigraphic cannot be underlined.

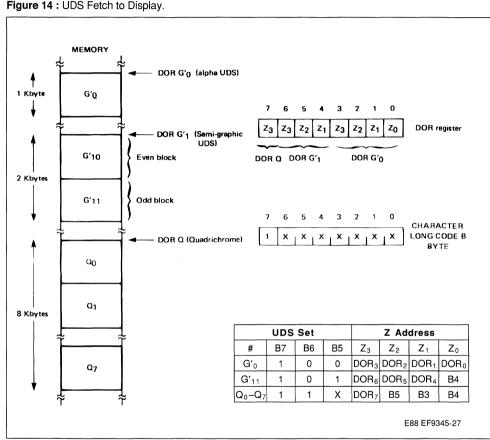

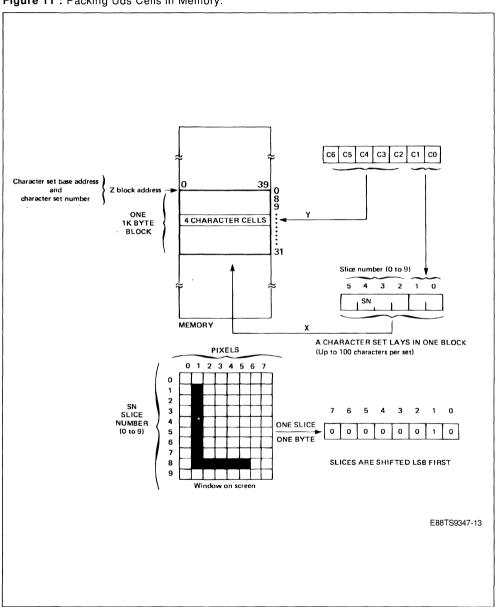

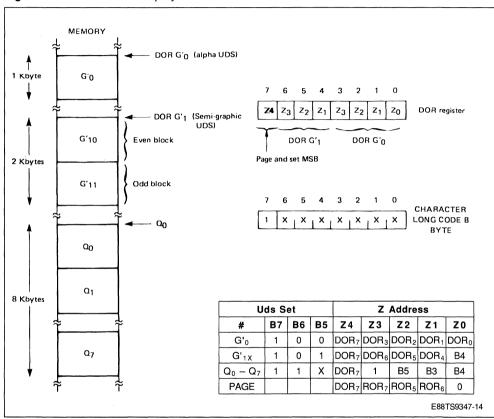

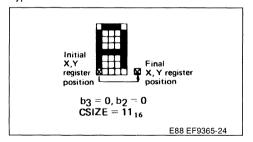

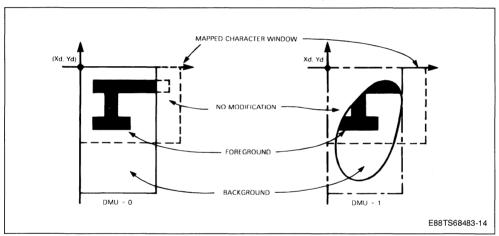

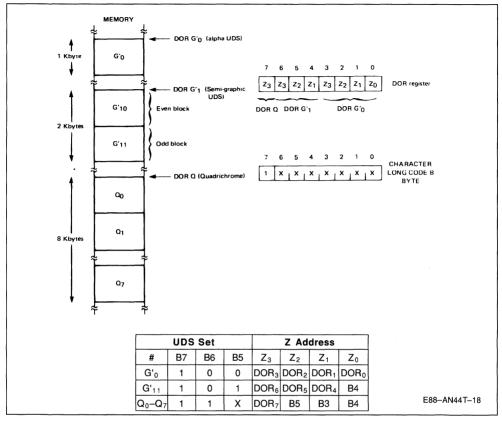

# **USED DEFINED CHARACTER GENERATOR IN MEMORY: DOR REGISTER**

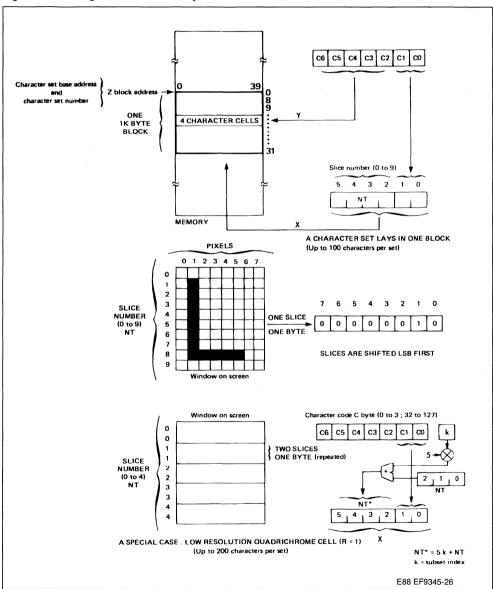

With 40 char /row, the elementary window dimensions on the screen are 10 slices x 8 pixels. Thus, a character cell holds 10 bytes in memory and 4 character cells are packed in one 40-byte buffer (fi-

gure 13). However, 5 bytes of a low resolution quadrichrome cell are enough to fill up to window. In this case, 8 character cells can be packed in one 40-byte buffer.

Figure 13: Packing UDS Cells in Memory.

The cells of one given character set should be layed in one block.

Up to 100 character cells may be addressed in each set (or 200 for low resolution quadrichrome only). The location in memory, where to fetch the sets in use, are declared by DOR register (figure 14). For

Elever 14 : LIDS Fotob to Display

each type of set, it gives the MSB(s) of the Z block address. EF9345 reads the Z LSB(s) in the B byte of the (equivalent) long code. As usual, the character code is read in the C byte. NT is derived from the TV line rank in the row and the double height status.

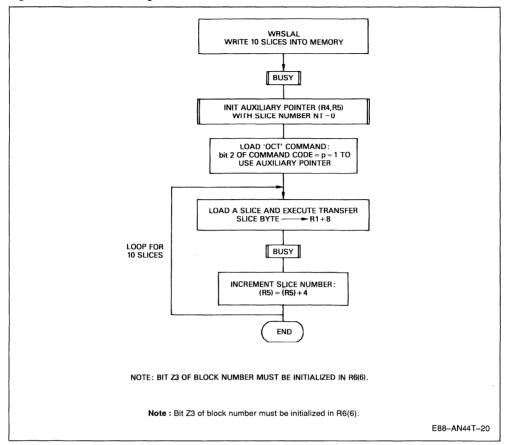

# LOADING USER DEFINED CHARACTER SET.

Before loading a character set into RAM, the user must:

- Assign a name to the set :

- G'<sub>0</sub>, G'<sub>10</sub> or G'<sub>11</sub> for bichrome characters.

- From Q0 to Q7 for quadrichrome characters.

- Assign a character number to each character belonging to this set, character numbers range from 0 to 3 and 32 to 127.

- It is binary coded into 7 bits C(0:6) C(0:6) will be loaded later on into a C byte character

- code in order to display the character.

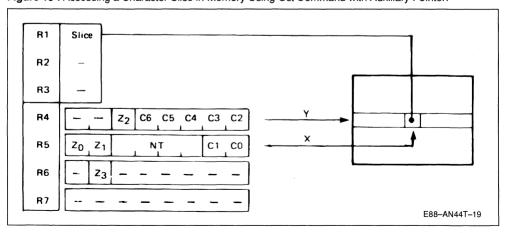

- A pointer to a character slice in memory is then manufactured from :

- the character number C(0:6)

- \_ the slice number NT(0:3)

- the block number assigned to the set Z(0:3).

Figure 15 shows how to proceed with the auxiliary pointer and the OCT command.

Note: The main pointer may be also used. When sequentially accessing slices of a given character, auto incrementation is helpless.

Figure 15: Accessing a Character Slice in Memory Using OCT Command with Auxiliary Pointer.

# ON-CHIP CHARACTER GENERATOR.

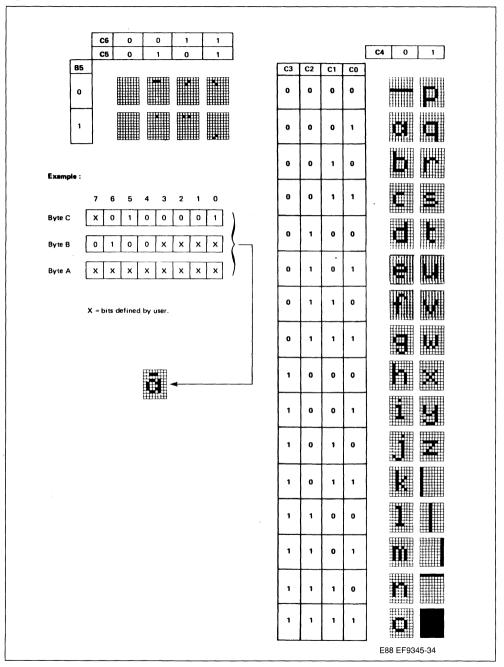

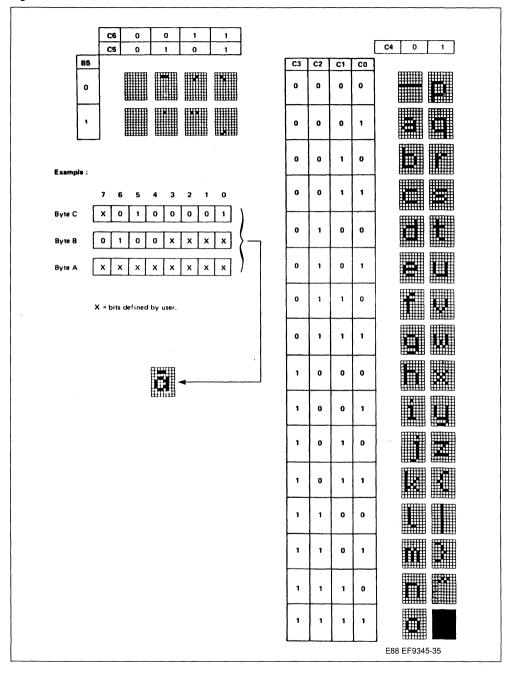

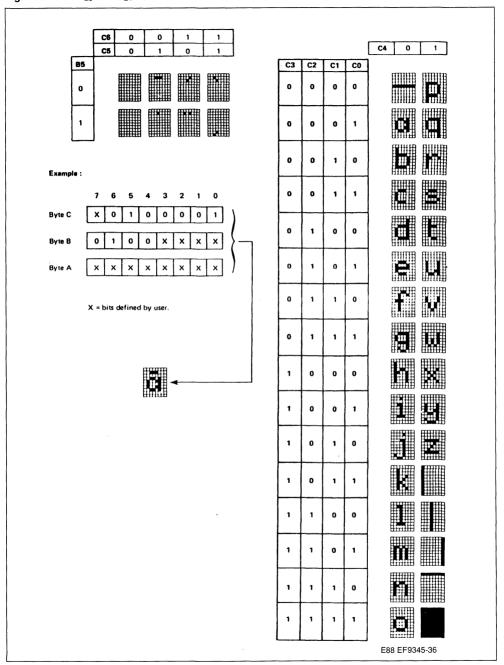

- G<sub>0</sub> set is common to 40 and 80 char./row modes (figure 16 and figure 25).

- G<sub>10</sub> is the standard mosaïc set for videotex (figure 17).

- G

G

11, G

20 and G

21 cannot be reached from the 16-bit short fixed codes (figure 18 and figure 19).

# DISPLAYING THE ATTRIBUTES.

- For normal operation, a double height and/or double width character must be repeated in memory in two successive Y and/or X positions. The user may otherwise freely mix any character size.

- 2. The attributes are logically processed in the following order:

- Underline or underline cursor: foreground forced on the last slice (NT = 9).

- Flash: background periodically forced on the whole window (0.5 Hz). The phase depends on the negative attribute.

- Conceal: background forced permanently on the whole window. A concealed character neither blinks nor is underlined.

- Negative: exchange the background and foreground color values when set.

- Coloring.

- Complemented cursor mode.

- Insert : black color forced when required.

- Basic pixel shift frequency: f<sub>CLK</sub> x 2/3 = 8 MHz.

Figure 16: G<sub>0</sub> Alphanumeric Character Set in 40 Character/Row Mode – EF9345.

|         |     |   |   | C6 | 0     | 0 | 0 | 0 | 1 | 1 | 1        | 1      |

|---------|-----|---|---|----|-------|---|---|---|---|---|----------|--------|

|         |     |   |   | C5 | 0     | 0 | 1 | 1 | 0 | ۰ | 1        | 1      |

|         |     |   |   | C4 | 0     | 1 | 0 | 1 | 0 | 1 | 0        | 1      |

| O<br>C3 | 0   | 0 | 0 |    |       | - |   | Ø | B |   |          |        |

| •       | •   | o | 1 |    |       |   |   |   | H |   | <b>u</b> |        |

| 0       | ٥   | 1 | 0 |    |       |   |   |   |   | Ħ |          |        |

| 0       | 0   | 1 | 1 |    |       |   |   | 3 |   |   |          |        |

| 0       | 1   | 0 | 0 |    |       |   |   |   |   |   |          |        |

| 0       | 1   | 0 | 1 | ,  |       |   |   |   |   |   |          |        |

| 0       | 1   | 1 | 0 |    |       |   |   |   |   |   |          |        |

| 0       | 1   | 1 | 1 |    |       |   |   |   |   |   |          |        |

| 1       | 0   | 0 | 0 |    |       |   |   |   |   |   |          |        |

| 1       | 0   | 0 | 1 |    |       |   |   |   |   |   |          |        |

| 1       | 0   | 1 | 0 |    |       |   |   |   |   |   |          |        |

| 1       | 0   | 1 | 1 |    |       |   |   |   |   |   |          |        |

| 1       | . 1 | 0 | 0 |    |       |   |   | K |   |   |          |        |

| 1       | 1   | 0 | 1 |    | TTTTT |   |   |   |   |   | m        |        |

| 1       | 1   | 1 | 0 |    |       |   |   |   |   |   |          |        |

| '       | 1   | 1 | 1 |    |       |   |   |   |   |   |          |        |

|         |     |   |   |    |       |   |   |   |   |   | E88      | EF9345 |

Figure 16 bis: G<sub>0</sub> Alphanumeric Character Set in 40 Character/Row Mode – EF9345 R003.

| C5 |    |    |          |    | C6 | 0 | 0 | 0       | 0  | 1 | 1        | 1 | 1            |

|----|----|----|----------|----|----|---|---|---------|----|---|----------|---|--------------|

|    |    |    |          |    |    |   |   |         |    |   |          |   | <del> </del> |

|    |    |    |          |    | C4 | 0 | 1 | 0       | 1  | 0 | 1        | 0 | 1            |

|    | C3 | C2 | C1       | Co | 1  |   |   | استسبيت |    |   | <b>4</b> | · | ·*           |

|    | 0  |    | 1        | 0  |    |   |   |         |    |   |          |   |              |

|    | 0  | 0  | 0        | 1  |    |   |   |         |    |   |          |   |              |

|    | 0  | 0  | ١,       |    |    | Ē | × |         |    |   |          |   |              |

|    | 0  | 0  | ,        | ,  |    |   |   |         |    |   |          |   |              |

|    | 0  | 1  | 0        | 0  |    |   |   |         |    |   |          |   |              |

|    | 0  | 1  | 0        | 1  |    |   |   |         | mm |   |          |   | -            |

|    | 0  | 1  | 1        | 0  |    |   |   |         |    |   |          |   |              |

|    | 0  | ,  | 1        | 1  |    |   |   |         |    |   |          |   |              |

|    | 1  | 0  | 0        | 0  |    |   | ä |         |    |   |          |   |              |

|    | 1  | 0  | 0        | ,  |    |   |   |         |    |   |          |   |              |

|    | 1  | 0  | ,        | •  |    |   |   |         |    |   |          |   |              |

|    | 1  | •  | <u> </u> | 1  |    |   |   |         |    | k |          | k |              |

|    | 1  | 1  | 0        | •  |    |   |   | -       |    |   |          |   |              |

|    | 1  | 1  | 0        | ļ. |    |   |   |         |    |   |          |   |              |

|    | 1  | 1  | 1        | 0  |    |   |   |         |    |   |          |   |              |

|    | 1  | ,  | <u> </u> | ١, |    |   | × |         |    |   |          |   |              |

Figure 16 ter: G<sub>0</sub> Alphanumeric Character Set in 40 Character/Row Mode – EF9345 R005.

|    |    |    |    |    | A |     |   |   |   |   |   |         |      |

|----|----|----|----|----|---|-----|---|---|---|---|---|---------|------|

|    |    |    | į  | C6 | 0 | 0   | 0 | 0 | 1 | 1 | 1 | 1       | 1    |

|    |    |    |    | C5 | 0 | 0   | 1 | 1 | 0 | 0 | 1 | 1       |      |

|    |    |    |    | C4 | 0 | 1   | 0 | 1 | 0 | 1 | 0 | 1       |      |

| :3 | C2 | C1 | CO |    |   |     |   |   |   |   |   |         | _    |

| 0  | 0  | 0  | 0  |    |   | ×   |   |   |   |   |   |         |      |

| 0  | 0  | 0  | 1  |    | • |     |   |   | H |   |   |         |      |

| 0  | o  | 1  | 0  |    |   |     |   |   | B |   |   |         |      |

| 0  | 0  | 1  | 1  |    | Ä |     | H |   |   |   |   |         |      |

| 0  | 1  | 0  | 0  |    |   |     |   |   |   |   |   |         |      |

| 0  | 1  | 0  | 1  |    |   |     |   |   |   |   |   |         |      |

| 0  | 1  | 1  | 0  |    |   | ŭ   | 8 |   |   |   |   |         |      |

| 0  | 1  | 1  | 1  |    |   | , 4 |   |   |   |   |   |         |      |

| 1  | 0  | 0  | 0  |    |   |     |   |   |   |   |   |         |      |

| 1  | 0  | 0  | 1  |    |   |     |   |   |   |   |   |         |      |

| 1  | 0  | 1  | 0  |    |   |     |   |   |   |   |   |         |      |

| 1  | 0  | 1  | 1  |    |   | ×   |   |   |   |   |   |         |      |

| 1  | 1  | 0  | 0  |    |   |     |   |   |   |   |   |         |      |

| 1  | 1  | 0  | 1  |    |   |     |   |   |   |   |   |         |      |

| 1  | 1  | 1  | 0  |    |   |     | _ |   |   |   |   |         |      |

| 1  | 1  | 1  | 1  |    |   |     |   |   |   |   |   |         |      |

|    |    |    |    |    |   |     |   |   |   |   | E | 88 EF93 | 15-3 |

Figure 17: G<sub>10</sub> Semigraphic Character Set.

|    |    |    |    |          | MOSA | IC Sem | i-graphic | : | SEPAF | RATED | Semi-gra | phic |

|----|----|----|----|----------|------|--------|-----------|---|-------|-------|----------|------|

|    |    |    |    | C6       | 1    | 1      | 1         | 1 | 0     | 0     | 0        | 0    |

|    |    |    |    | C5<br>C4 | 0    | 1      | 0         | 1 | 0     | 0     | 0        | 1    |

| C3 | C2 | C1 | CO |          |      |        | L         | L | L     | 1     |          | 1    |

| 0  | 0  | 0  | 0  |          |      |        |           |   |       |       |          |      |

| 0  | 0  | 0  | 1  |          |      |        |           |   |       |       |          |      |

| 0  | 0  | 1  | 0  |          |      |        |           |   |       |       |          |      |

| 0  | 0  | 1  | 1  |          |      |        |           |   |       |       |          |      |

| 0  | 1  | 0  | 0  |          |      |        |           |   |       |       |          |      |

| 0  | 1  | 0  | 1  |          |      |        |           |   |       |       |          |      |

| 0  | 1  | 1  | 0  |          |      |        |           |   |       |       |          |      |

| 0  | 1  | 1  | 1  |          |      |        |           |   |       |       |          |      |

| 1  | 0  | 0  | 0  |          |      |        |           |   |       |       |          |      |

| 1  | 0  | 0  | 1  |          |      |        |           |   |       |       |          |      |

| 1  | 0  | 1  | 0  |          |      |        |           |   |       |       |          |      |

| 1  | 0  | 1  | 1  |          |      |        |           |   |       |       |          |      |

| 1  | 1  | 0  | 0  |          |      | ::::   |           |   |       |       |          |      |

| 1  | 1  | 0  | 1  |          |      |        |           |   |       |       |          |      |

| 1  | 1  | 1  | 0  |          |      |        |           |   |       |       |          |      |

| 1  | 1  | 1  | 1  |          |      |        |           |   |       |       | E        |      |

Figure 18: G<sub>11</sub> Stroke Set.

|    |    |    |    | <b>C5</b> 0 | 0     |

|----|----|----|----|-------------|-------|

| СЗ | C2 | C1 | CO | C4 0        | 1 1   |

| o  | 0  | 0  | 0  |             |       |

| 0  | 0  | 0  | 1  |             |       |

| 0  | 0  | 1  | 0  |             |       |

| 0  | 0  | 1  | 1  |             |       |

| 0  | 1  | 0  | 0  |             |       |

| 0  | 1  | o  | 1  |             |       |

| 0  | 1  | 1  | 0  |             |       |

| o  | 1  | 1  | 1  |             |       |

| 1  | 0  | 0  | 0  | 7           |       |

| 1  | 0  | 0  | 1  |             |       |

| 1  | 0  | 1  | 0  |             |       |

| 1  | 0  | 1  | 1  |             |       |

| 1  | 1  | 0  | 0  |             |       |

| 1  | 1. | 0  | 1  |             |       |

| 1  | 1  | 1  | 0  |             |       |

| 1  | 1  | 1  | 1  |             |       |

|    |    |    |    | -           | E88 E |

Figure 19: G<sub>20</sub> and G<sub>21</sub> Accentued Character Sets for 9345.

Figure 19 bis: G<sub>20</sub> and G<sub>21</sub> Accentued Character Sets for 9345 – R003.

Figure 19 ter: G<sub>20</sub> and G<sub>21</sub> Accentued Character Sets for 9345 – R005.

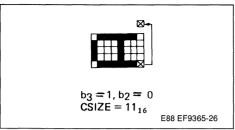

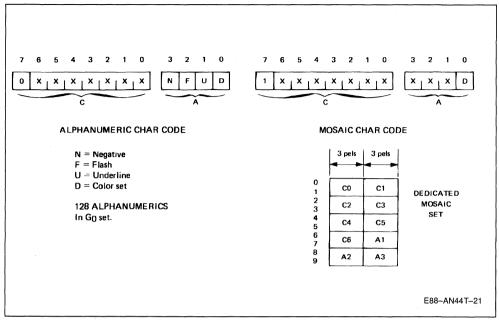

# 80 CHAR/ROW CHARACTER CODES

To display pages in 80 character per row format, one of two character code formats must be selected.

- Long (12 bits) code: 4 parallel attributes and large on-chip 1024 semigraphic character set,

- Short (8 bits) code : no attribute, no semigraphic set

Both formats address the on-chip  $G_0$  set (128 characters 6 x 10). None allows UDS addressing.

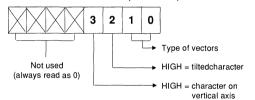

# LONG CODES.

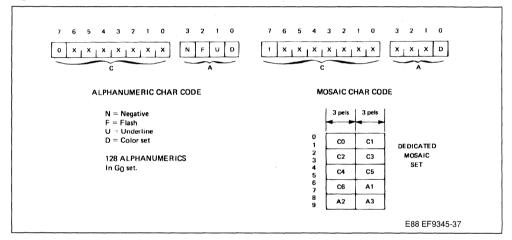

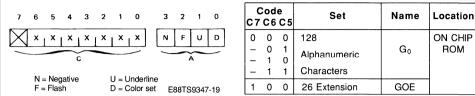

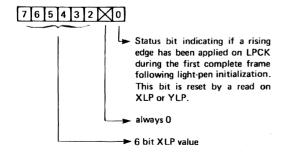

Each 6 pixels x 10 lines character window on the screen is associated with a 12-bit code in memory, namely a C byte and an attribute nibble A (figure 10). C7 bit designates the set.

- Alphanumeric set : C7 = 0.

- C(0:6) designates one out of 128 alphanumeric characters in the G<sub>0</sub> on-chip set. This set is common to the 40 char/row format, with the 2 right most columns truncated (see figure 25).

- A(0:3) gives 4 parallel attributes.

- Mosaïc set : C7 = 1.

A(1:3) and C(0:6) address a dedicated mosaïc character. Each of these address bits controls the foreground/background status of a 3 pixels x 2 lines sub-window: foreground when the bit is set.

A0 provides a color select attribute.

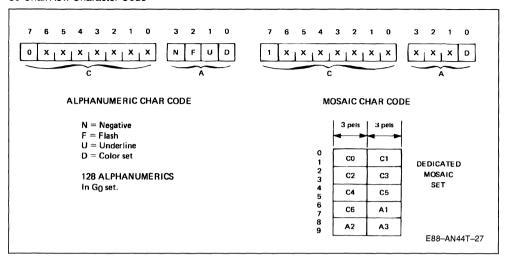

Figure 20: 80 Char/Row Character Code.

# SHORT CODES.

They are derived from the long code by giving a 0 implicit value to each bit of the A nibble : positive, not underlined, not flashing.

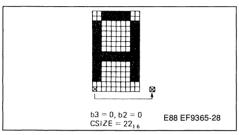

# PACKING THE CODES IN MEMORY.

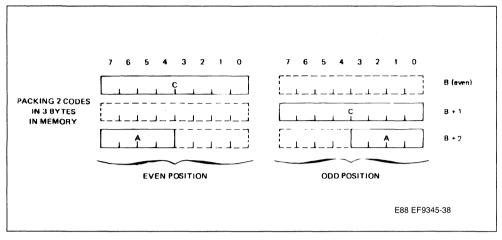

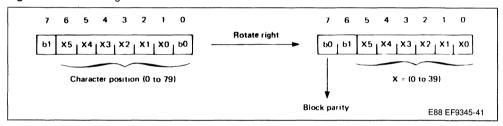

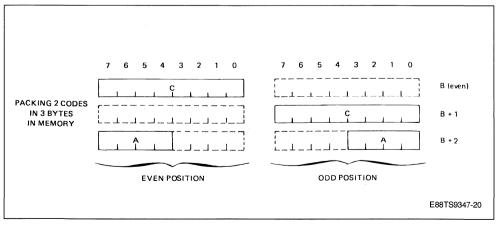

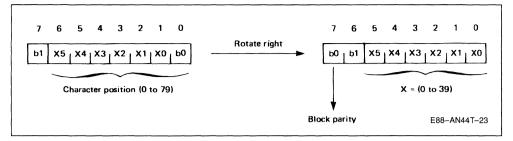

Long codes are paired. A pair is packed in a 3-byte word. Therefore, the 80 codes of a row fill a 120-byte row buffer (figure 21). The left most position on the screen is even. Its corresponding C byte is at the beginning of the first buffer. The next position on the screen is odd. Its corresponding C byte is at the beginning of the second buffer. Both nibbles are packed in the third buffer. With short codes, the same scheme yields 80-byte row buffers.

# ACCESS TO THE CODES IN MEMORY.

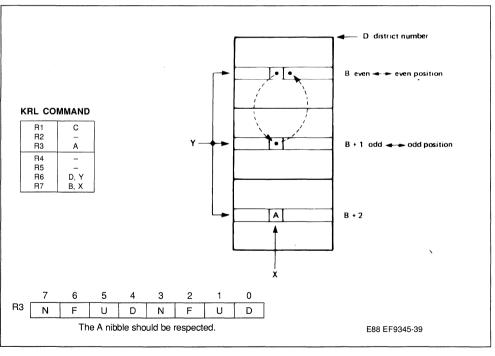

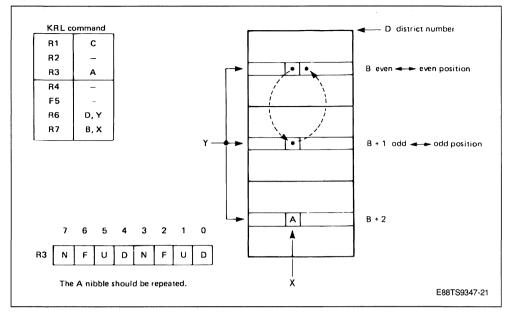

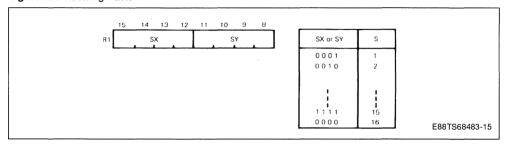

KRL command transfers 12 bits from/to the R1 and R3 registers to/from memory. The read modify write operation, necessary to write the A nibble in memory, is automatically performed provided that the A nibble is repeated in the R3 register (figure 22). Dedicated auto-incrementation is also performed when required.

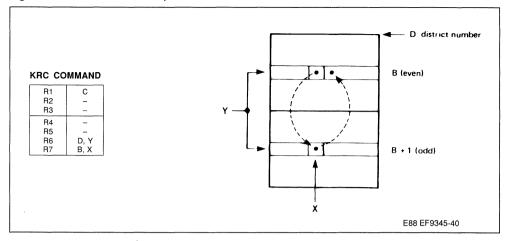

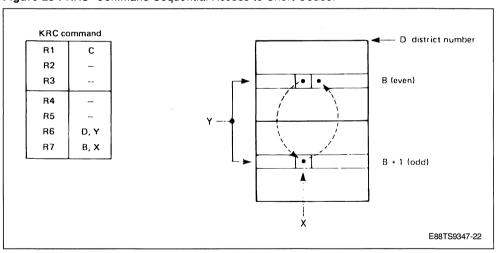

KRC command does a similar job for the short codes (figure 23).

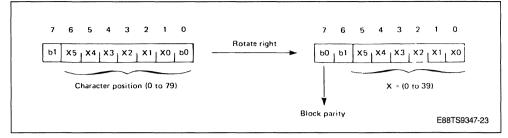

A very simple scheme allows the microprocessor to transcode an horizontal screen location into a pointer (figure 24). The joint use of this scheme with the dedicated command alleviates all the packing/unpacking troubles.

Figure 21: 80 Char/Row Code Packing.

Figure 22: KRL Command: Sequential Access to Long Codes.

Figure 23: KRC Command: Sequential Access to Short Codes.

Figure 24: Transcoding an Horizontal Screen Location into a R7 Pointer.

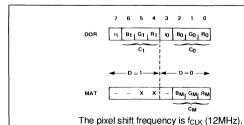

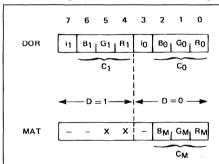

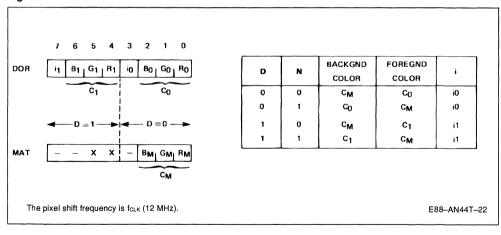

DISPLAYING THE ATTRIBUTES - DOR REGISTER.

Short code and mosaïc characters are not flashing, not underlined and "positive".

The attributes are processed in the following order:

- Underline or underlined cursor: foreground is forced on the last slice (NT = 9).

- Flash: background is periodically (0.5 Hz – 50%) forced on all the window. The phase depends on the negative attribute.

- Color select: a "positive" character is displayed with a background color same as the margin color. The foreground color is selected in DOR register by the D attribute.

- Negative: when the character is negative, background and foreground colors are exchanged. In complemented CURSOR position, these colors are complemented.

- Insert: the D attribute selects one insert value in DOR register. This attribute is then processed up to the current insertion mode (see screen format and attribute insert section).

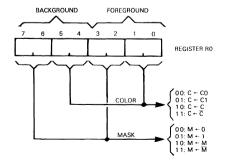

| D | N | BACKGND<br>COLOR | FOREGND<br>COLOR                 | i  |

|---|---|------------------|----------------------------------|----|

| 0 | 0 | См               | C <sub>0</sub>                   | i0 |

| 0 | 1 | C₀<br>Cм         | С <sub>0</sub><br>С <sub>м</sub> | i0 |

| 1 | 0 | C <sub>M</sub>   | C <sub>1</sub>                   | i1 |

| 1 | 1 | C <sub>1</sub>   | C <sub>M</sub>                   | i1 |

E88 EF9345-42

Figure 25: G<sub>0</sub> Alphanumeric Character Set in 80 Character/Row Mode – EF9345.

|    |    |    |    |          | <b>,</b> |                    |                   |                    |         |          |         |       |

|----|----|----|----|----------|----------|--------------------|-------------------|--------------------|---------|----------|---------|-------|

|    |    |    |    | C7       | 0        | 0                  | 0                 | 0                  | 0       | 0        | 0       | 0     |

|    |    |    |    | C6       | 0        | 0                  | 0                 | 0                  | 1       | 1        | 1       | 1     |

|    |    |    |    | C5<br>C4 | 0        | 1                  | 0                 | 1                  | 0       | 0        | 1       | 1     |

|    |    |    |    | <u></u>  |          | <u> </u>           |                   | <u> </u>           |         | <u> </u> | 0_      | 1     |

| C3 | C2 | C1 | CO | ł        |          | <del>(11111)</del> | <del>111111</del> | <del>(TTOTT)</del> | 1770071 | puu:     | 1111111 | (#### |

| ·  | °  | •  | 0  |          |          |                    |                   | O                  | E       | P        |         |       |

| 0  | 0  | •  | 1  |          |          |                    |                   |                    |         |          |         |       |

| 0  | 0  | 1  | 0  |          |          |                    |                   |                    | B       | R        | b       |       |

| 0  | 0  | 1  | ,  |          | £        |                    | Ħ                 |                    |         |          |         | #     |

| 0  | 1  | 0  | 0  |          | ä        |                    |                   |                    |         |          |         |       |

| 0  | 1  | ۰  | 1  |          |          |                    |                   |                    |         |          |         |       |

| 0  | 1  | 1  | 0  |          | Ë        |                    |                   |                    |         | *        | ř       |       |

| 0  | 1  | 1  | 1  |          | Ä        |                    |                   |                    |         |          |         |       |

| 1  | o  | 0  | 0  |          |          |                    |                   |                    |         |          |         |       |

| 1  | o  | 0  | 1  |          | Ë        | *                  |                   |                    |         |          |         |       |

| 1  | 0  | 1  | 0  |          |          |                    | ×                 |                    |         |          |         |       |

| 1  | 0  | 1  | 1  |          |          |                    |                   |                    |         |          |         |       |

| 1  | 1  | 0  | 0  |          |          |                    |                   | ď.                 |         |          |         |       |

| 1  | 1  | 0  | 1  |          |          |                    |                   |                    |         |          |         |       |

| 1  | 1  | 1  | 0  |          |          |                    |                   |                    |         |          |         |       |

| '  | 1  | 1  | 1  |          |          | Š                  |                   |                    |         |          |         |       |

|    |    |    |    |          |          |                    |                   |                    |         |          |         |       |

SGS-THOMSON MICROELECTRONICS

Figure 25 bis: G<sub>0</sub> Alphanumeric Character Set in 40 Character/Row Mode – EF9345 R003.

|     |    |    |    | C7 | 0  | 0 | 0 | 0 | 0 | 0        | 0  | 0 |

|-----|----|----|----|----|----|---|---|---|---|----------|----|---|

|     |    |    |    | C6 | 0  | 0 | 0 | 0 | 1 | 1        | 1  | 1 |

|     |    |    |    | C5 | 0  | 0 | 1 | 1 | 0 | 0        | 1  | 1 |

|     |    |    |    | C4 | 0  | 1 | 0 | 1 | 0 | <u>'</u> | 10 | 1 |

| СЗ  | C2 | C1 | CO | ]  |    |   |   |   |   |          |    |   |

| 0   | 0  | 0  | o  |    |    |   |   |   |   |          |    |   |

| , 0 | 0  | 0  | 1  |    |    |   |   |   |   |          |    |   |

| 0   | 0  | 1  | 0  |    |    | # |   |   |   | R        |    |   |

| 0   | o  | ,  | ,  |    |    |   | # |   |   |          |    |   |

| 0   | 1  | 0  | 0  |    |    |   |   |   |   |          |    |   |

| 0   | 1  | 0  | 1  |    |    |   |   |   |   |          |    |   |

| 0   | 1  | ,  | 0  |    |    |   |   |   |   |          |    |   |

| 0   | ,  | 1  | 1  |    |    |   |   |   |   |          |    |   |

| ,   | •  | 0  | 0  |    |    |   |   |   |   |          |    |   |

| 1   | o  | 0  | 1  |    |    |   |   |   |   |          |    |   |

| 1   | 0  | ,  | o  |    |    |   |   |   |   |          |    |   |

| 1   | o  | 1  | 1  |    |    |   |   |   |   |          |    |   |

| 1   | 1  | 0  | o  |    | *  |   |   |   |   |          |    |   |

| 1   | 1  | 0  | 1  |    |    |   |   |   |   |          |    |   |

| 1   | 1  | 1  | 0  |    |    |   |   |   |   |          |    |   |

| 1   | 1  | 1  | 1  |    | Į. | * | M |   |   |          |    |   |

|     |    |    |    |    |    |   |   |   |   |          |    |   |

40/50

Figure 25 ter: G<sub>0</sub> Alphanumeric Character Set in 40 Character/Row Mode – EF9345 R005.

|    |    |    |     |    | r 1 |     |   |   | — т | т        | 7 |          |

|----|----|----|-----|----|-----|-----|---|---|-----|----------|---|----------|

|    |    |    |     | C7 | 0   | 0   | 0 | 0 | 0   | 0        | 0 | _0       |

|    |    |    |     | C6 | 0   | 0   | 0 | 0 | 1   | <u>'</u> | 1 | <u>'</u> |

|    |    |    |     | C5 | 0   | 0   | 1 | 1 | 0   | 0        | 1 | 1        |

|    |    |    |     | C4 | 0   | _1_ | 0 | 1 | 0   | 1        | 0 | '        |

| 23 | C2 | C1 | CO  | ]  |     |     |   |   |     |          |   |          |

| 0  | 0  | 0  | 0   |    | *** |     |   |   |     |          |   |          |

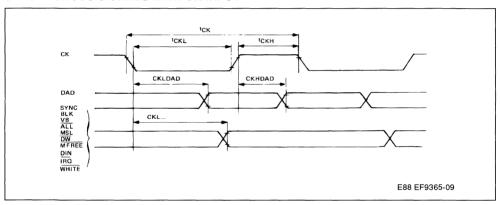

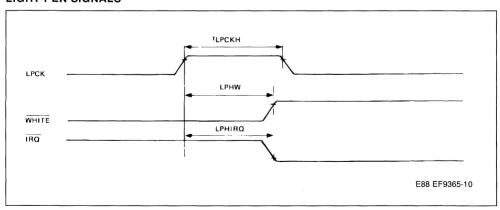

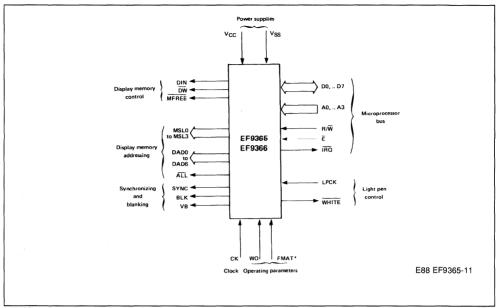

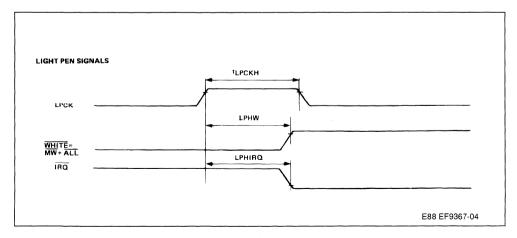

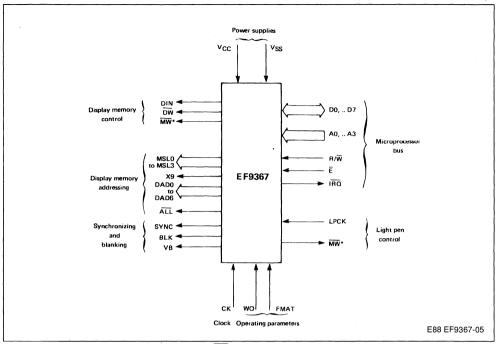

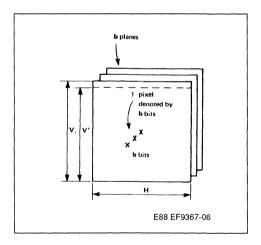

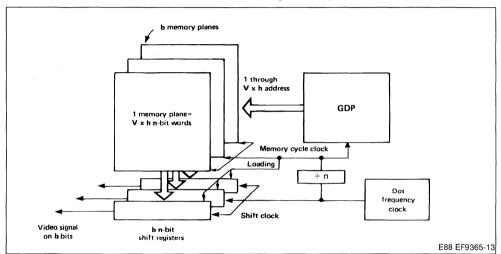

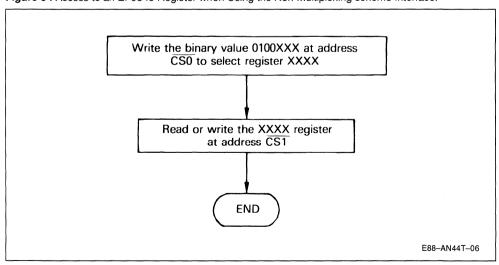

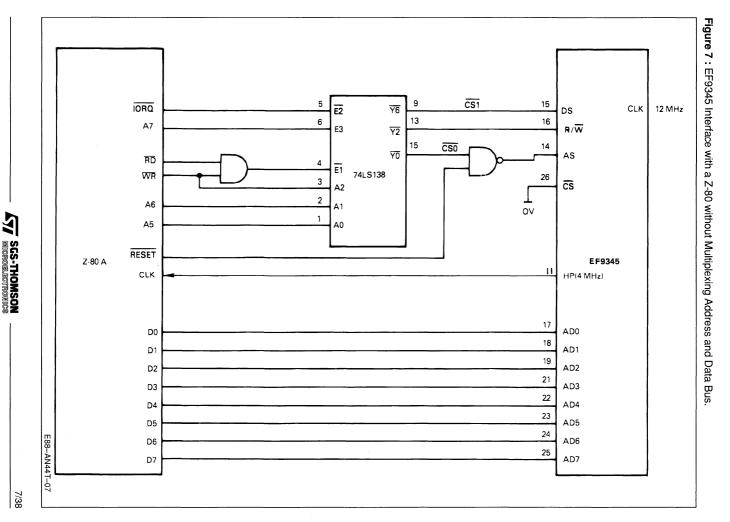

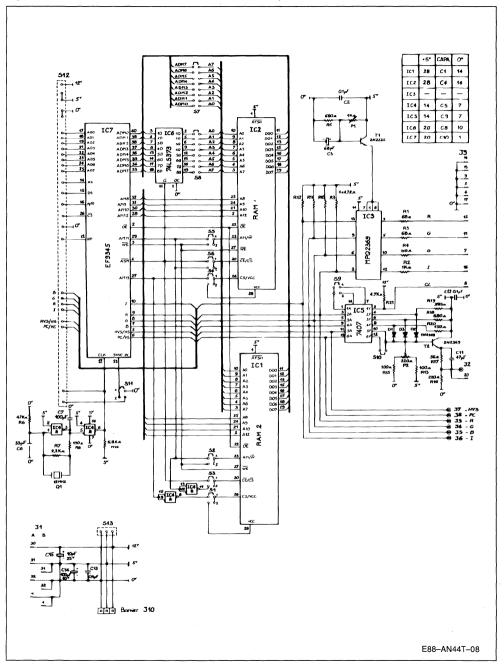

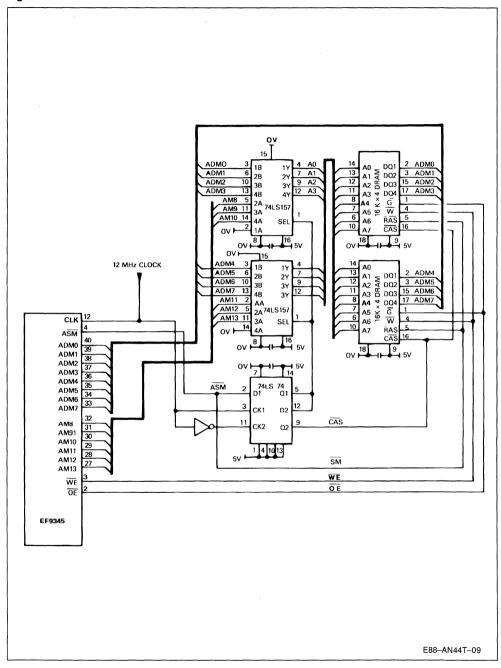

| 0  | 0  | 0  | 1   |    |     |     |   |   |     |          |   |          |